## TRABALHO DE GRADUAÇÃO

# ESTUDO E DESENVOLVIMENTO DE UMA FERRAMENTA-BASE PARA CRIAÇÃO DE PROCESSADORES DE APLICAÇÃO ESPECÍFICA

Moysés Pinheiro Nery

Brasília, dezembro de 2020

#### UNIVERSIDADE DE BRASILIA

Faculdade de Tecnologia Curso de Graduação em Engenharia de Controle e Automação

## TRABALHO DE GRADUAÇÃO

## ESTUDO E DESENVOLVIMENTO DE UMA FERRAMENTA-BASE PARA CRIAÇÃO DE PROCESSADORES DE APLICAÇÃO ESPECÍFICA

### Moysés Pinheiro Nery

Relatório submetido como requisito parcial de obtenção de grau de Engenheiro de Controle e Automação

#### Banca Examinadora

| Prof.         | Dr.          | Jones Yudi Mori Alves da Silva,          |  |

|---------------|--------------|------------------------------------------|--|

| ENM/<br>Orien | UnB<br>tador |                                          |  |

|               |              | Daniel Mauricio Muñoz Arboleda, rinterno |  |

| Prof.         | Dr. R        | enato Coral Sampaio, FGA/UnB             |  |

| Exami         | nador        | r interno                                |  |

Brasília, dezembro de 2020

#### FICHA CATALOGRÁFICA

#### MOYSÉS, PINHEIRO NERY

Estudo e desenvolvimento de uma ferramenta-base para criação de processadores de aplicação específica,

[Distrito Federal] 2020.

51p., 297 mm (FT/UnB, Engenheiro, Controle e Automação, 2020). Trabalho de Graduação – Universidade de Brasília. Faculdade de Tecnologia.

1. Back-end LLVM

- 2. Compiladores

- 3. Processadores de aplicação específica

- I. Mecatrônica/FT/UnB

#### REFERÊNCIA BIBLIOGRÁFICA

NERY, MOYSÉS PINHEIRO, (2020). Estudo e desenvolvimento de uma ferramenta-base para criação de processadores de aplicação específica. Trabalho de Graduação em Engenharia de Controle e Automação, Publicação FT.TG- $n^{\circ}0XX$ , Faculdade de Tecnologia, Universidade de Brasília, Brasília, DF, 51p.

#### CESSÃO DE DIREITOS

AUTOR: Moysés Pinheiro Nery

TÍTULO DO TRABALHO DE GRADUAÇÃO: Estudo e desenvolvimento de uma ferramentabase para criação de processadores de aplicação específica.

GRAU: Engenheiro ANO: 2020

É concedida à Universidade de Brasília permissão para reproduzir cópias deste Trabalho de Graduação e para emprestar ou vender tais cópias somente para propósitos acadêmicos e científicos. O autor reserva outros direitos de publicação e nenhuma parte desse Trabalho de Graduação pode ser reproduzida sem autorização por escrito do autor.

Moysés Pinheiro Nery

Grupo de Automação e Controle - Universidade de Brasília.

70910-900 - Brasília - DF - Brasil.

### Agradecimentos

Gostaria de agradecer primeiramente a Deus, que é tudo para mim e sem o qual eu não sou nada. Agradeço também a cada um dos professores, monitores, colegas de turmas que me ajudaram a trilhar minha trajetória acadêmica e a enfrentar cada obstáculo que surgiu. Em especial agradeço ao Professor Jones Yudi pela sua grandiosa ajuda e dedicação durante a orientação deste projeto. Agradeço ainda aos amigos e familiares que sempre me incentivaram cada um de sua maneira. Agradeço aos meus pais, Anísio e Rosângela, por todo o apoio e suporte que me condicionaram a chegar até aqui. Por fim, agradeço à Sophia, minha dedicada, atenciosa e conselheira esposa, por ter sido, a cada dia, minha fonte de inspiração e motivação a seguir em frente.

Moysés Pinheiro Nery

#### **RESUMO**

Os sistemas embarcados estão difundidos em quase todos os aspectos do cotidiano da atualidade. Esses sistemas encontram-se em smartphones, videogames, câmeras inteligentes, carros elétricos, fábricas automatizadas e diversas outras aplicações. Por conta disso diversos microprocessadores são desenvolvidos a cada dia para desempenharem certo grupo específico de aplicações, de modo que é necessário acompanhar tais arquiteturas de processadores com seus respectivos compiladores. Este trabalho objetiva estudar o desenvolvimento de um compilador realizado para uma arquitetura computacional didática chamada de "Cpu0", que é um microprocessador RISC de 32 bits, cujo código em Verilog é aberto ao público, onde o framework LLVM foi utilizado para criação de um backend para portar tal arquitetura de um novo compilador. Além disso, busca-se realizar modificações no backend a fim de adequá-lo a possíveis alterações na ISA do Cpu0 para aplicá-lo a um contexto específico. O LLVM é uma estrutura de compilação modular que foi concebida para compilar softwares de forma otimizada, por meio do fornecimento de informações de alto nível às transformações do compilador que levam a tempos de compilação e execução otimizados.

Palavras Chave: LLVM, Backend, processadores, compiladores

#### ABSTRACT

Embedded systems are widespread in almost all aspects of today's daily life. These systems are found in smartphones, video games, smart cameras, electric cars, automated factories and several other applications. Because of this, several microprocessors are developed every day to perform a specific group of applications, so it is necessary to add to these processor architectures with their respective compilers. This work aims to study the development of a compiler made for a didactic computational architecture called "Cpu0", which is a 32-bit RISC microprocessor, whose code in Verilog is open to the public, where the LLVM framework was used to create a backend to port such architecture to a new compiler. In addition, modifications are made to the backend in order to adapt it to possible changes in the Cpu0 ISA to apply it to a specific context. The LLVM is a modular compilation structure that was designed to compile software in an optimized way, by providing high-level information to the compiler transformations that lead to optimized compilation and execution times.

Keywords: LLVM, Backend, processors, compilers

## **SUMÁRIO**

| 1        | Introd | lução                                  | 1  |

|----------|--------|----------------------------------------|----|

|          | 1.1    | Contextualização                       | 1  |

|          | 1.2    | Objetivos do projeto                   | 4  |

|          | 1.3    | Apresentação do manuscrito             | 5  |

| <b>2</b> | A estr | rutura do LLVM                         | 6  |

|          | 2.1    | Introdução                             | 6  |

|          | 2.2    | LLVM IR: a representação intermediária | 6  |

|          | 2.3    | Compilação em três fases               | 7  |

|          | 2.3.1  | FRONTENDS                              | 8  |

|          | 2.3.2  | Otimizador                             | 9  |

|          | 2.3.3  | BACKENDS                               | 9  |

|          | 2.4    | Geração do código de máquina           | 9  |

|          | 2.4.1  | Etapas da geração de código            | 10 |

|          | 2.4.2  | TableGen                               | 11 |

| 3        | O mic  | roprocessador Cpu0                     | 13 |

|          | 3.1    | Banco de registradores                 | 13 |

|          | 3.2    | Conjunto de instruções                 | 14 |

|          | 3.2.1  | Instruções tipo A                      | 15 |

|          | 3.2.2  | Instruções tipo L                      | 15 |

|          | 3.2.3  | Instruções tipo J                      | 15 |

|          | 3.2.4  | O registrador de status (SW)           | 17 |

|          | 3.3    | Caminho de dados                       | 18 |

| 4        | O Bac  | kend LLVM Cpu0                         | 19 |

|          | 4.1    | Informações gerais do backend          | 21 |

|          | 4.2    | Seleção de instruções                  | 22 |

|          | 4.2.1  | Construção do DAG inicial              | 23 |

|          | 4.2.2  | Otimização do DAG inicial              | 24 |

|          | 4.2.3  | Legalização do DAG                     | 25 |

|          | 4.2.4  | Seleção de instruções                  | 28 |

|          | 4.3    | Escalonamento de Instruções            | 33 |

|    | 4.4     | Alocação dos registradores                     | 34 |

|----|---------|------------------------------------------------|----|

|    | 4.5     | Inserção do prólogo e epílogo                  | 37 |

|    | 4.6     | Emissão do código                              | 37 |

|    | 4.7     | Integração ao LLVM                             | 38 |

| 5  | Modifie | cações, Testes e Resultados                    | 39 |

|    | 5.1     | Verificação do backend no simulador de Verilog | 39 |

|    | 5.2     | Omitindo uma instrução do backend              | 45 |

|    | 5.3     | Inserindo uma instrução no backend             | 47 |

| 6  | Conclu  | sões                                           | 50 |

|    | 6.1     | Perspectivas Futuras                           | 50 |

| RI | EFERÊI  | NCIAS BIBLIOGRÁFICAS                           | 51 |

## LISTA DE FIGURAS

| 1.1  | Esquemático do ASIP Designer extraído de [1]                                   | 2  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | Esquemático da arquitetura do Xtensa LX7, última versão lançada da plataforma  |    |

|      | Tensilica Xtensa, extraído de [2]                                              | 3  |

| 1.3  | Esquemático do fluxo de desenvolvimento da TCE extraido de [3]                 | 4  |

| 2.1  | Código C de duas funções que adicionam dois números                            | 7  |

| 2.2  | Código LLVM IR gerado a partir do código em C da Figura 2.1                    | 7  |

| 2.3  | Estrutura de compilação em três fases do LLVM                                  | 8  |

| 2.4  | Passos de geração de código a partir do LLVM [4]                               | 11 |

| 3.1  | Estrutura do processador Cpu0, extraído de [5]                                 | 13 |

| 3.2  | Formato das instruções do microprocessador Cpu0                                | 14 |

| 3.3  | Formato das instruções tipo A                                                  | 15 |

| 3.4  | Formato das instruções tipo L                                                  | 15 |

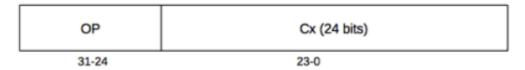

| 3.5  | Formato das instruções tipo J                                                  | 15 |

| 3.6  | Formato do registrador SW                                                      | 17 |

| 4.1  | Hierarquia das principais classes que compõem o backend do Cpu0                | 20 |

| 4.2  | Implementação da classe CpuTargetMachine que integra o backend                 | 21 |

| 4.3  | Implementação da classe CpuSubtarget que integra o backend                     | 22 |

| 4.4  | Código LLVM IR da função modulo<br>Diferenca utilizada como exemplo durante o  |    |

|      | processo de geração de código de máquina                                       | 22 |

| 4.5  | DAG inicial do bloco "inicio" da função modulo<br>Diferenca                    | 23 |

| 4.6  | DAG otimizado do bloco "inicio" da função modulo<br>Diferenca                  | 25 |

| 4.7  | Convenções de chamada de função adotadas na construção do backend LLVM Cpu0.   | 26 |

| 4.8  | Trecho de código da Cpu0TargetLowering que trata a transformação manual de     |    |

|      | GlobalAdresses.                                                                | 27 |

| 4.9  | DAG legalizado do bloco "inicio" da função modulo<br>Diferenca                 | 28 |

| 4.10 | Implementação da classe de instruções genérica dentro do escopo da TableGen    | 29 |

| 4.11 | Implementação da classe de formato de instruções do tipo A dentro do escopo da |    |

|      | TableGen                                                                       | 29 |

| 4.12 | Implementação da classe de formato de instruções do tipo L dentro do escopo da |    |

|      | TableGen                                                                       | 30 |

| 4.13 | Implementação da classe de formato de instruções do tipo J dentro do escopo da TableGen | 3 |

|------|-----------------------------------------------------------------------------------------|---|

| 111  | Formato da instrução ADD.                                                               | • |

|      | Formato da instrução ORi                                                                | , |

|      | Definição da instrução ADD dentro do escopo da TableGen                                 | , |

|      | •                                                                                       | , |

| 4.17 | Implementação da classe ArithLogicR, classe utilizada para definir as instruções        |   |

| 110  | logicas e aritméticas cujos operandos são somente registradores.                        | , |

|      | Definição do operando imediato utilizado pela instrução ORi.                            | , |

|      | Definição da instrução ORi dentro do escopo da TableGen                                 | , |

| 4.20 | Implementação da classe ArithLogicI, classe utilizada para definir as instruções        |   |

|      | logicas e aritméticas cujos operandos são registradores e valores imediatos             |   |

|      | DAG final do bloco "inicio" da função modulo Diferenca                                  | , |

| 4.22 | Código gerado a partir do bloco "inicio"da função modulo<br>Diferenca após etapa        |   |

|      | "Escalonamento de Instruções"                                                           | • |

| 4.23 | Implementação da classe Cpu0Reg utilizada para definir os registradores do Cpu0         |   |

|      | dentro do escopo da TableGen.                                                           | , |

| 4.24 | Definição do banco de registradores do Cpu0 dentro do escopo da TableGen                | , |

| 4.25 | Definição das classes de registradores do Cpu0 dentro do escopo da TableGen             | , |

| 4.26 | Código gerado a partir do bloco "inicio" da função modulo<br>Diferenca após a etapa     |   |

|      | "Alocação de registradores".                                                            | • |

| 4.27 | Código gerado a partir do bloco "inicio"<br>da função modulo<br>Diferenca após a etapa  |   |

|      | "Inserção do prólogo e epílogo"                                                         | , |

| 4.28 | Código final em assembly gerado a partir da função modulo<br>Diferenca                  |   |

| 4.29 | Método de registro do backend Cpu0 ao LLVM                                              | , |

| 5.1  | Código em C da função que soma dois números quaisquer                                   |   |

| 5.2  | Código em LLVM IR da função que soma dois números quaisquer                             |   |

| 5.3  | Código em $assembly$ da função que soma dois números quaisquer                          | 4 |

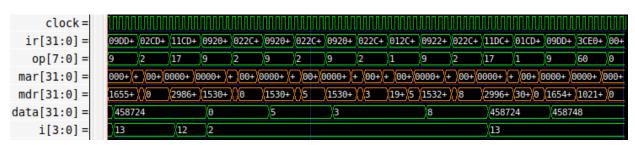

| 5.4  | Resultado obtido da simulação da execução do código da Figura 5.3                       | 2 |

| 5.5  | Código em C da função que testa a estrutura if-else                                     | 2 |

| 5.6  | Código em LLVM IR da função que testa a estrutura if-else                               | 2 |

| 5.7  | Código em $\it assembly$ da função que testa a estrutura if-else                        | 2 |

| 5.8  | Resultado obtido da simulação da execução do código da Figura 5.5                       | 2 |

| 5.9  | Código em C que testa a chamada de função                                               | 2 |

| 5.10 | Código em LLVM IR da função main.                                                       | 2 |

| 5.11 | Código em LLVM IR da função funcSoma                                                    | 2 |

|      | Código em assembly da função main                                                       | 2 |

|      | Código em assembly da função funcSoma                                                   | 2 |

|      | Resultado obtido da simulação da execução do código da Figura 5.9 (1 de 2)              | 2 |

|      | Resultado obtido da simulação da execução do código da Figura 5.9 (2 de 2)              | 2 |

|      | Código LLVM IR utilizado para verificar a omissão de instruções de multiplicação        | 4 |

| -0   | O                                                                                       |   |

| 5.17 | Mensagem de erro obtido ao omitir as definições de instruções de multiplicação no                                         |    |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

|      | backend Cpu0                                                                                                              | 45 |

| 5.18 | ${\bf Comandos} \ Set Operation Action \ {\bf para} \ {\bf expandir} \ {\bf instruções} \ {\bf de} \ {\bf multiplicação}$ | 46 |

| 5.19 | Código em assembly da função da Figura 5.16                                                                               | 46 |

| 5.20 | Código em C da função mulsi3                                                                                              | 47 |

| 5.21 | Operação da instrução MAC                                                                                                 | 47 |

| 5.22 | Implementação da classe MACFormat                                                                                         | 48 |

| 5.23 | Definição da instrução MAC no arquivo Cpu0InstrInfo                                                                       | 48 |

| 5.24 | Função MACTest em LLVM IR utilizada para verificar a implementação da instru-                                             |    |

|      | ção MAC                                                                                                                   | 48 |

| 5.25 | Código assembly gerado a partir da Figura 5.24                                                                            | 49 |

## LISTA DE TABELAS

| 3.1 | Lista de registradores do Cpu0                         | 14 |

|-----|--------------------------------------------------------|----|

| 3.2 | Conjunto de instruções da Cpu032I                      | 16 |

| 3.3 | Instruções adicionadas no Cpu032II a partir do Cpu032I | 17 |

## LISTA DE SÍMBOLOS

## Siglas

ABI Application Binary Interface

ASIP Application-Specific Instruction Set Processor

CISC Complex Instruction Set Computer

CPU Unidade Central de Processamento - Central Processing Unit

DAG Directed Acyclic Graph

FPGA Field Programmable Gate Array

GCC Gnu Compiler Collection

IR Intermediate Representation

ISA Instruction Set Architecture

LLVM Low Level Virtual Machine

MVT Machine Value Type

RISC Reduced Instruction Set Computer

SSA Static Single Assignment

SoC System On a Chip

## Capítulo 1

## Introdução

## 1.1 Contextualização

Os grandes avanços tecnológicos da indústria microeletrônica conseguiram, nas últimas décadas, disseminar a utilização de sistemas de computação para aplicações diversas. Temas atuais, como a Internet das Coisas e a Indústria 4.0, realçam a tendência de adoção de sistemas embarcados. O desempenho de um sistema embarcado é determinado por diversos fatores, tais como: velocidade de processamento, consumo de energia, custo, segurança e confiabilidade, entre outros. Os processadores comumente encontrados no mercado são de uso genérico, oferecendo um desempenho médio apenas razoável. Uma forte tendência tecnológica é a adoção de processadores de aplicação específica, ou seja, processadores desenvolvidos com foco em um domínio de aplicação. Um exemplo são os DSPs (Processadores Digitais de Sinais), os quais possuem instruções e blocos de hardware específicos para os algoritmos da área, como as instruções MAC (Multiply-And-Accumulate).

Processadores de aplicação específica são, geralmente, baseados em arquiteturas comuns adaptadas para melhoria de métricas de desempenho (em custo, velocidade, consumo de energia, etc.). Então essas adaptações das arquiteturas devem focar em um domínio de aplicação (telecomunicações, processamento de imagens, inteligência artificial, controle, etc), ou mesmo em aplicações específicas (codificador H264, OCR, reconhecimento de impressão digital, controle PID clássico, etc).

Um dos tipos de processadores de aplicação específica que existe é o ASIP (Application-Specific Instruction Set Processor), em que existem instruções criadas especialmente para aquele domínio de aplicação, como o caso da instrução MAC, muito utilizada em DSPs. Atualmente, duas ferramentas comerciais dominam o mercado da área:

- ASIP Designer

- Tensilica xTensa

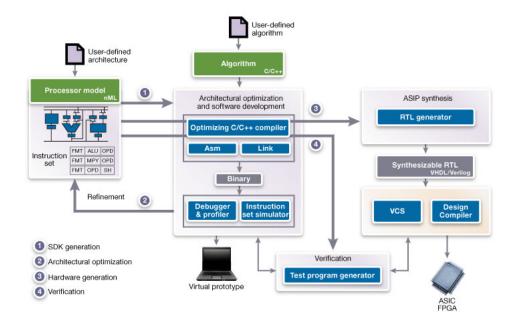

- O ASIP Designer da Synopsys é um conjunto de ferramentas utilizadas na criação de pro-

cessadores customizados [1]. Os principais recursos incluem a rápida exploração de escolhas de arquitetura, geração de um kit de desenvolvimento de software baseado em compilador C/C++ eficiente que se adapta automaticamente a cada mudança na arquitetura e geração automática de RTL ( $Register-Transfer\ Level$ ) sintetizável.

Figura 1.1: Esquemático do ASIP Designer extraído de [1].

Conforme a Figura 1.1, a tecnologia do ASIP Designer oferece suporte à modelagem de arquiteturas de conjunto de instruções ASIP na linguagem de descrição de processador nML. O nML é uma linguagem de definição de alto nível para descrever uma arquitetura de processador e um conjunto de instruções (ISA). Ainda, oferece a tecnologia de compilador em loop, permitida pela geração automática de um kit de desenvolvimento de software (SDK) abrangente para cada ASIP modelado em nML, contendo componentes como um compilador otimizador, reconhecido por sua geração de código eficiente e retargetability rápida e automática para novas arquiteturas ASIP, um linker, que constrói um arquivo executável a partir de arquivos de objeto ELF, um assembler e dissambler, que traduz o código de máquina da montagem para o formato binário e vice-versa. Ainda, o ASIP Designer vem com uma ampla variedade de exemplos de designs ASIP, permitindo aos desenvolvedores criar rapidamente seu próprio ASIP visando seus requisitos de aplicação específicos.

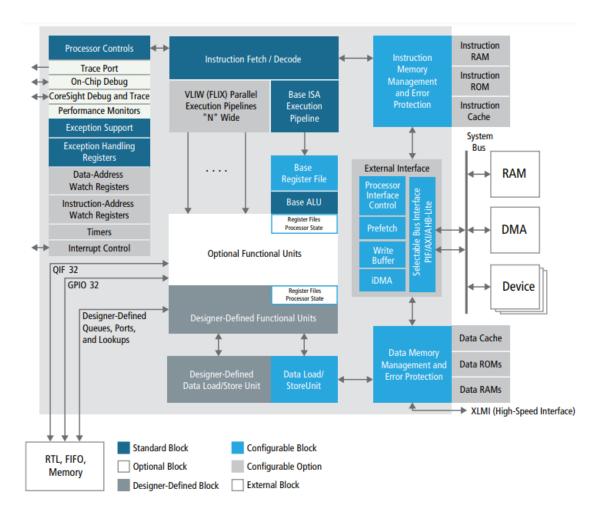

De forma semelhante, a Tensilica xTensa, da Cadence, é uma ferramenta de geração automática de processadores customizados para aplicações específicas, sendo pioneira neste tipo de mercado [6].

Figura 1.2: Esquemático da arquitetura do Xtensa LX7, última versão lançada da plataforma Tensilica Xtensa, extraído de [2].

Essa ferramenta é bastante flexível, disponibilizando opções de configuração a depender da necessidade do desenvolvedor, conforme Figura 1.2. Além disso, é possível estender a arquitetura base por meio da metodologia *Tensilica Instruction Extension* (TIE). A linguagem TIE pode ser usada para descrever instruções, registradores, unidades funcionais que são adicionados automaticamente para o processador. A linguagem TIE é uma linguagem semelhante a Verilog usado para descrever os mnemônicos de instrução desejados, operandos, codificação e semântica de execução. Arquivos TIE são entradas para o gerador de processadores Xtensa. O gerador automaticamente constrói o processador e a cadeia completa de ferramentas de software que incorpora todas as opções de configuração e novas instruções TIE.

Algumas ferramentas acadêmicas também oferecem processadores customizáveis:

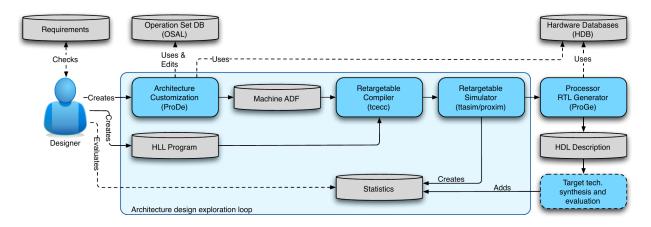

- TCE (TTA-based Co-Design Environment)

- LegUp

A TCE vem sendo desenvolvida como *opensource* há mais de 10 anos na Universidade de Tampere, Finlândia. Esse projeto é um conjunto de ferramentas que pode ser usado para projetar

e programar processadores personalizados com base na *Transport Triggered Architecture* (TTA) [3]. O conjunto de ferramentas fornece um fluxo de co-design *retargetable* completo de programas de linguagem de alto nível até o processador RTL sintetizável (backends VHDL e Verilog são suportados) e binários de programa paralelos. Os pontos de personalização do processador incluem o banco de registradores, as unidades funcionais, instruções suportadas e a rede de interconexão.

Figura 1.3: Esquemático do fluxo de desenvolvimento da TCE extraido de [3].

A LegUp é uma ferramenta open source cuja principal característica é a geração automática de aceleradores em hardware, para um processador baseado em FPGA (Field Programmable Gate Array). Essa plataforma permite sintetizar um programa padrão em C em uma arquitetura de processador/acelerador híbrida baseada em FPGA que consiste em um processador se comunicando com aceleradores de hardware personalizados [7]. Dessa maneira, ao compilar uma aplicação em C, a ferramenta analisa a aplicação e gera aceleradores para algumas partes do código. Para isso, ela particiona a aplicação em uma parte para software encapsulada em um programa maior com entradas/saídas; uma parte para hardware, com síntese automática de VHDL/Verilog. Assim, ao final é obtido um processador comum com um acelerador acoplado.

Um dos grandes desafios da criação de processadores de aplicação específica é a criação dos respectivos compiladores, sem os quais dificulta-se muito a implementação de algoritmos complexos. Existem muitos compiladores disponíveis para as mais diversas linguagens de programação, no entanto, a maioria desses compiladores destinam-se a um sistema operacional específico, ou arquitetura preexistente. Não obstante, existem projetos que permitem desenvolver um backend de compilador para novas arquiteturas, onde entre eles encontra-se o LLVM.

## 1.2 Objetivos do projeto

A proposta deste trabalho é estudar o framework LLVM, com ênfase no processo de desenvolvimento de um backend deste framework para uma nova arquitetura computacional, tendo como referência o backend desenvolvido para o microprocessador didático Cpu0 [8]. Além disso, objetiva-se realizar modificações no referido compilador de modo a refletir possíveis alterações

realizáveis em processadores de aplicação específica. Os resultados desse projeto servirão de base para o desenvolvimento de uma ferramenta de geração de arquiteturas hardware/software para aplicações específicas.

## 1.3 Apresentação do manuscrito

Este trabalho está redigido em seis capítulos.

O Capítulo 1 compreende a introdução e apresenta a contextualização, motivações e objetivos a serem alcançados com o trabalho.

No Capítulo 2 é realizada uma descrição da estrutura do LLVM e dos seus principais componentes, com enfoque no processo de geração de código.

No Capítulo 3 encontra-se uma apresentação da organização e arquitetura do processador didático CPU0, bem como a descrição completa do seu conjunto de instruções e caminho de dados.

O Capítulo 4 descreve a implementação do backend LLVM para o processador CPU0, seus principais componentes e forma que os mesmos interagem entre si.

O Capítulo 5 compreende a fase de testes, modificações realizadas e resultados do trabalho.

Por fim, o Capítulo 6 corresponde à conclusão, onde todo o projeto será analisado e possíveis encaminhamentos serão propostos.

## Capítulo 2

## A estrutura do LLVM

## 2.1 Introdução

O LLVM é um framework de compiladores construído na linguagem C++ e concebido para otimizar a compilação de programas a partir da sua representação intermediária de código, na qual são realizadas diversas transformações que conduzem a uma redução nos tempos de compilação e execução. Começou a ser desenvolvido em 2000 por Chris Lattner na University of Illinois, como tema de sua dissertação de mestrado [9], e passou a ser um software open source em 2003, tornando-se um projeto em desenvolvimento contínuo que conta com o apoio de grandes empresas como Intel, Google, Adobe, Apple, entre outras. LLVM é um acrônimo para Low Level Virtual Machine, que representava inicialmente sua linguagem intermediária, o que não faz mais sentido visto que o projeto expandiu-se e engloba muitos outros subprojetos [10].

O LLVM vem ganhando grande popularidade entre os desenvolvedores, sendo utilizado em projetos acadêmicos e comerciais. Uma das principais razões para isso é o fato de não ser apenas um compilador, mas sim uma estrutura de compilação baseada em bibliotecas, o que fornece aos seus usuários uma grande flexibilidade, uma vez que seus módulos operam funções específicas e possuem grande independência entre si.

## 2.2 LLVM IR: a representação intermediária

A característica mais importante da infraestrutura do LLVM é a sua representação intermediária LLVM IR. A LLVM IR é uma linguagem própria, com semântica bem definida.

A LLVM IR é uma representação semelhante a de um conjunto de instruções de um processador RISC (Reduced-instruction-set Computing), contendo instruções simples como add, sub, compare, branch, entre outras, mas apresentando informações de alto nível que conduzem às otimizações realizadas pelo LLVM. A LLVM IR suporta labels; possui um sistema de tipos de dados interno que suporta inteiros, ponto flutuante, booleanos, vetores, structures, entre outros; trabalha sobre um número ilimitado de registradores virtuais; pode ser representada em três variações: textual

(extensão .ll) na forma SSA (Single Static Assignment), binária (extensão .bc) e uma estrutura de dados "in-memory" (do inglês, "em memória"). A descrição completa da linguagem LLVM IR pode ser encontrada no LLVM Language Manual Reference [11]. A Figura 2.1 ilustra um código escrito em C e a Figura 2.2 ilustra sua versão correspondente em LLVM IR.

```

unsigned add1(unsigned a, unsigned b) {

return a+b;

}

//perhaps not the most efficient way to add two numbers

unsigned add2(unsigned a, unsigned b) {

if(a == b) return b;

return add2(a-1, b+1);

}

```

Figura 2.1: Código C de duas funções que adicionam dois números.

```

define i32 @add1(i32 %a, i32 %b) {

entrv:

%tmp1 = add i32 %a, %b

ret i32 %tmp1

}

define i32 @add2(i32 %a, i32 %b) {

%tmp1 = icmp eq i32 %a, 0

br i1 %tmp1, label %done, label %recurse

recurse:

tmp2 = sub i32 %a,

%tmp3 = add i32 %b,

%tmp4 = call i32 @add2(i32 %tmp2, i32 %tmp3)

ret i32 tmp4

done:

ret i32 %b

}

```

Figura 2.2: Código LLVM IR gerado a partir do código em C da Figura 2.1

## 2.3 Compilação em três fases

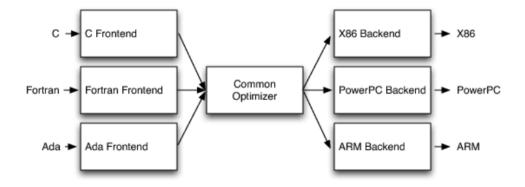

Assim como a maioria dos compiladores tradicionais, o LLVM adota o projeto de compilador em três fases, conforme Figura 2.3.

Inicialmente, o frontend recebe o código fonte como entrada e realiza as análises léxica e sintática, transformando o código na representação intermediária LLVM IR que independe da linguagem do código fonte. Após isso, o otimizador realiza uma série de transformações que visam reduzir o tempo de execução, por exemplo eliminando instruções redundantes. Por fim, o backend gera o código de máquina, passando, principalmente, pelas etapas de seleção e escalonamento das instruções, alocação de registradores, otimizações finais e emissão do código de máquina, em formato assembly ou binário.

Figura 2.3: Estrutura de compilação em três fases do LLVM

#### 2.3.1 frontends

O LLVM não inclui nenhum frontend para uma linguagem específica. No entanto, sua equipe desenvolveu dois frontends oficiais que são disponibilizados separadamente: GCC-LLVM e Clang. Apesar disso, por ser um framework aberto, há atualmente uma grande comunidade desenvolvendo outros frontends para linguagens como Fortran, Haskell, Ruby, etc. O funcionamento de um frontend LLVM se concentra basicamente em transformar o código de uma linguagem de programação para a linguagem LLVM IR.

#### 2.3.1.1 LLVM-GCC

Como desenvolver um frontend para uma linguagem de programação é uma tarefa bastante trabalhosa e não trivial, a equipe do LLVM decidiu construir o LLVM-GCC, que se baseia no conjunto de frontends preexistentes do GCC 4.2 da Apple. O LLVM-GCC é projetado para transformar o código escrito na linguagem intermediária do GCC, chamada GIMPLE, na linguagem intermediária do LLVM, chamada LLVM IR, de modo que os frontends do GCC funcionem também como frontends do LLVM. A principal desvantagem dessa abordagem é o fato de o frontend do GCC ser lento e consumir bastante memória.

#### 2.3.1.2 Clang

Diferentemente do LLVM-GCC, o Clang é um frontend desenvolvido inteiramente pela equipe do LLVM. Atualmente suporta as linguagens C, C++, Objective-C, Objective-C++, OpenCL, CUDA e RenderScript [12]. Em comparação com o GCC, o Clang apresenta as seguintes vantagens [13][14]:

- Fornece o diagnóstico de erros e cuidados mais claro e descritivo.

- É muito mais rápido e utiliza menos memória.

- Como toda estrutura do LLVM, é modular, extensível, reutilizável.

As desvantagens notáveis em relação ao GCC são o fato de suportar menos linguagens e ser menos popular na comunidade colaborativa.

#### 2.3.2 Otimizador

As otimizações realizadas pelo LLVM independem tanto da linguagem do código fonte quanto da arquitetura para a qual será gerado o código de máquina pelo backend. A partir do código gerado pelo frontend na representação intermediária, são realizadas uma sequência de análises e transformações pelo otimizador do LLVM gerando um código IR mais eficiente e com mesma semântica. Cada uma dessas análises ou transformações são realizadas por algoritmos modulares chamados de *Pass*, de modo a dar liberdade ao projetista para escolher quais operações de otimização serão utilizadas em seu projeto dentre o rol de operações disponibilizadas pelo LLVM.

Para cada uma das formas de apresentação do código em LLVM IR o framework fornece ferramentas para realizar as otimizações padrões. A API "Pass-Manager API" disponibiliza operações de otimização caso o código LLVM IR esteja na forma "in-memory". No caso das formas textual ou binária, a ferramenta opt é utilizada para operar as otimizações.

#### 2.3.3 backends

O backend tem a função de transformar o código em LLVM IR para o código de máquina da arquitetura alvo. O LLVM oferece um *framework* de geração de código [4] que disponibiliza algoritmos comuns ao processo de geração de código para todas as arquiteturas, como seleção de instrução, alocação dos registradores, entre outros. A seção a seguir descreve as principais etapas da geração de código e apresenta uma descrição do *framework* de geração de código da LLVM.

## 2.4 Geração do código de máquina

O gerador de código da LLVM é composto essencialmente por um conjunto de componentes reutilizáveis que permitem a tradução do código em representação intermediária para o código de máquina. Entre eles, pode-se destacar os seguintes [4]:

- Um conjunto de interfaces abstratas que percebem aspectos importantes das características de uma determinada arquitetura alvo;

- Classes utilizadas para representar o processo de geração do código independentemente da arquitetura alvo;

- Classes que modelam o código independentemente da arquitetura alvo.

#### 2.4.1 Etapas da geração de código

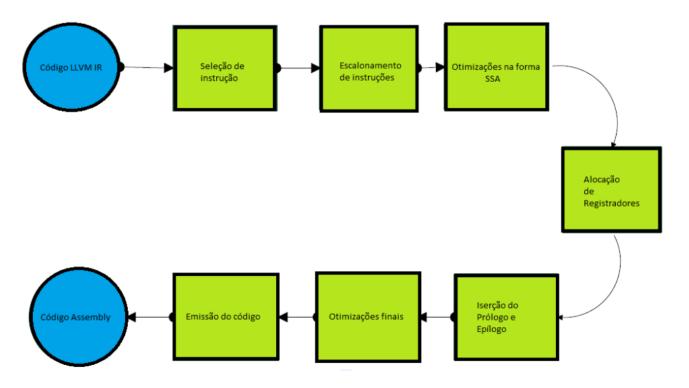

O processo de geração de código a partir do framework é realizado em sete etapas, conforme a Figura 2.4:

- 1. Seleção de instrução: primeiramente, o código LLVM IR é transformado de modo a utilizar as instruções da máquina alvo. O processo de seleção de instrução adotado pela LLVM consiste nos seguintes passos:

- (a) O primeiro passo consiste em transformar o código LLVM em um Grafo Acíclico Direcionado (DAG) chamado de "ilegal" pois utiliza instruções e tipos de dados não suportados pela máquina alvo.

- (b) Após isso, algumas otimizações são realizadas para simplificar o grafo.

- (c) Busca-se, então, legalizar o grafo, a fim de substituir as instruções e tipos de dados que não são suportados pela máquina alvo.

- (d) Algumas outras otimizações são realizadas a fim de eliminar redundâncias geradas após a legalização do grafo.

- 2. Escalonamento de instruções: a partir do DAG legalizado obtido na etapa anterior, as instruções são reordenadas de modo a satisfazer eventuais restrições da máquina alvo, como por exemplo uma quantidade mínima de registradores disponível em qualquer momento do programa.

- 3. Otimizações na forma SSA: esta etapa é opcional e consiste em realizar uma série de otimizações no código em SSA, tais como *modulo-scheduling* ou *peephole*.

- 4. Alocação de registradores: as referências aos registradores virtuais da LLVM IR são redirecionadas aos registradores reais da máquina alvo.

- 5. Inserção do prólogo e epílogo: uma vez que o código de máquina já foi gerado e o tamanho da pilha necessário já é conhecido, o prólogo e epílogo já podem ser inseridos no código.

- 6. Otimizações finais: última etapa de otimização, que serve para eliminar eventuais redundâncias que permanecem no código de máquina.

- 7. Emissão do código: por fim, o código em linguagem de máquina é emitido, completando o processo de compilação.

Figura 2.4: Passos de geração de código a partir do LLVM [4]

No desenvolvimento do backend para um novo processador, uma descrição da arquitetura deve ser fornecida ao framework de geração de código para que as etapas acima possam funcionar corretamente. Isso é feito pela implementação de classes que são escritas a partir das classes abstratas fornecidas pelo framework. No entanto, cada uma dessas classes utiliza informações que são comuns entre si, o que acaba conduzindo a redundâncias de código, sujeitando o desenvolvedor a cometer erros facilmente. Diante disso, o LLVM disponibiliza a ferramenta TableGen do LLVM, que busca contornar essa situação.

#### 2.4.2 TableGen

A TableGen [15] é uma ferramenta que é usada para descrever diversos aspectos da arquitetura reduzindo a quantidade de repetição de código. Essa ferramenta gera os códigos em C++ a partir de códigos de descrição que descrevem detalhadamente as características da máquina alvo escritos em sintaxe própria da ferramenta. Componentes como registradores, instruções, convenções de chamadas são descritos a partir da sua estrutura.

A sintaxe utilizada pela TableGen consiste em duas partes principais: classes e definições, onde ambas são chamadas de records. As classes são formas abstratas dos records e são utilizadas para descrever e construir outros records. As definições são instâncias das classes, sendo por isso a forma concreta de um record, contendo uma identificação e atribuindo valores aos seus atributos. A TableGen fornece classes abstratas a partir dos quais se pode construir os códigos de descrição da máquina alvo.

É importante salientar que a TableGen não gera todos os componentes necessários, sendo

preciso implementar alguns deles separadamente para se ter o backend completo.

## Capítulo 3

## O microprocessador Cpu0

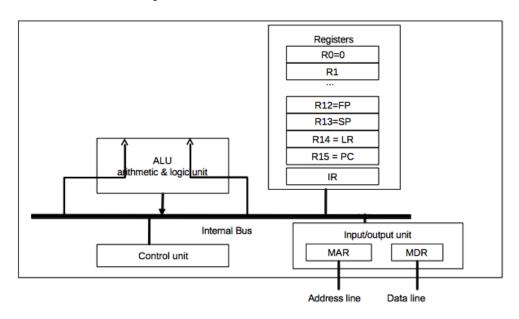

O Cpu0 é uma arquitetura de microprocessador de 32 bits desenvolvida pelo professor Chen Zhongcheng, da Golden Gate University [5], para fins didáticos. A Figura 3.1 ilustra os principais componentes da estrutura do Cpu0.

Figura 3.1: Estrutura do processador Cpu0, extraído de [5]

### 3.1 Banco de registradores

O banco de registradores é constituído por 16 registradores de 32 bits, os quais são enumerados de R0 a R15. O registrador R0 contém sempre o valor zero. Os registradores de R1 a R10 são de uso geral. O registrador R11 corresponde ao *Global Pointer Register* (GP), que aponta para o endereço de memória reservado às variáveis estáticas declaradas no programa em execução. O registrador R12 corresponde ao *Frame Pointer Register* (FP), que aponta para o endereço de memória reservado aos procedimentos. O registrador R13 corresponde ao *Stack Pointer Register*

| Registrador                    | Descrição                                                                |

|--------------------------------|--------------------------------------------------------------------------|

| R0                             | Valor fixado em zero                                                     |

| R1-R10                         | Registradores de uso geral                                               |

| R11                            | Global Pointer register (GP)                                             |

| R12                            | Frame Pointer register (FP)                                              |

| R13                            | Stack Pointer register (SP)                                              |

| R14                            | Link Register (LR)                                                       |

| R15                            | Status Word Register (SW)                                                |

| IR                             | Instruction Register                                                     |

| MAR                            | Memory Address Register (MAR)                                            |

| MDR Memory Data Register (MDR) |                                                                          |

| HI                             | Guarda os 32 bits mais significativos do resultado de uma multiplicação  |

| LO                             | Guarda os 32 bits menos significativos do resultado de uma multiplicação |

Tabela 3.1: Lista de registradores do Cpu0

(SP), que aponta para o endereço base de memória da pilha. O registrador R14 corresponde ao Link Register (LR), que armazena o endereço da próxima instrução a ser executada após uma instrução de salto. Por fim, o registrador R15 corresponde ao Status Word Register (SW), que armazena o estado dos campos Negative (N), Zero (Z), Carry (C), Overflow (V), Debug (D), Mode (M), e Interrupt (I), que são sinalizadores que servirão para, entre outras coisas, determinar se um desvio será feito ou não.

Além dos registradores mencionados acima, há também outros registradores reservados de uso específico, como o *Program Counter Register* (PC), que contém o endereço de memória da instrução a ser executada, o *Instruction Register* (IR), que armazena a instrução em execução, entre outros. A Tabela 3.1 apresenta a lista completa dos registradores do Cpu0.

## 3.2 Conjunto de instruções

A arquitetura de conjunto de instruções do Cpu0 foi construída baseada no paradigma RISC e admite três tipos de instruções: instruções de operações lógicas ou aritméticas classificadas como instruções "tipo A", instruções de acesso à memória que formam a classe de instruções "tipo L" e instruções de desvios do fluxo de execução, chamadas de instruções "tipo J". As instruções operam em, no máximo, très operandos e possuem o tamanho fixo de 32 bits. O formato dos três tipos de instruções é semelhante, conforme ilustrado na Figura 3.2, o que facilita a decodificação das instruções.

| Opcode [31-24] | Operandos, registrador de destino e sinais de seleção [23-0] |

|----------------|--------------------------------------------------------------|

Figura 3.2: Formato das instruções do microprocessador Cpu0

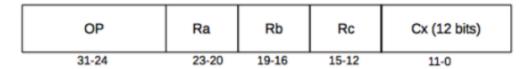

### 3.2.1 Instruções tipo A

As operações lógicas e aritméticas são realizadas apenas em registradores, ou entre um registrador e um valor imediato. O formato desse tipo de instruções é representado na Figura 3.3.

Figura 3.3: Formato das instruções tipo A

${\cal O}$  campo  ${\cal C}x$  é utilizado para guardar valores de deslocamentos de bits ou deslocamento de endereços.

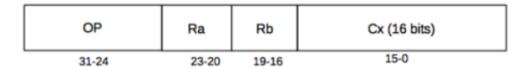

### 3.2.2 Instruções tipo L

As operações de acesso à memória são efetuadas pelas instruções LOAD e STORE. O formato das instruções tipo L é representado pela Figura 3.4. Nestas instruções, o endereço da memória a ser acessado é obtido pela soma entre Rb e Cx.

Figura 3.4: Formato das instruções tipo L

#### 3.2.3 Instruções tipo J

Os desvios de fluxo de execução, também chamados de saltos, são tomados ou não a partir do conteúdo do registrador SW (*Status Word*), no qual são guardados resultados de comparações entre dois registradores operandos, conforme descrito anteriormente. O campo Cx contém o deslocamento de endereço do salto em relação ao PC. O formato das instruções tipo J é ilustrado na Figura 3.5.

Figura 3.5: Formato das instruções tipo J

O modelo de arquitetura da Cpu0 admite dois conjuntos de instruções: Cpu032II e Cpu032II. A grande diferença entre esses conjuntos de instruções é que a CPUO32II engloba todas as instruções presentes no CPUO32II e acrescenta outras. As Tabelas 3.2 e 3.3 retratam as listas das instruções presentes em cada um dos conjuntos de instruções.

Tabela 3.2: Conjunto de instruções da Cpu<br/>032 I

| Formato | Mnemônico | Descrição                          | Sintaxe          |

|---------|-----------|------------------------------------|------------------|

| L       | NOP       | No Operation                       |                  |

| L       | LD        | Load word                          | LD Ra, [Rb+Cx]   |

| L       | ST        | Store word                         | ST Ra, [Rb+Cx]   |

| L       | LB        | Load byte                          | LB Ra, [Rb+Cx]   |

| L       | LBu       | Load byte unsigned                 | LBu Ra, [Rb+Cx]  |

| L       | SB        | Store byte                         | SB Ra, [Rb+Cx]   |

| L       | LH        | Load half word                     | LH Ra, [Rb+Cx]   |

| L       | LHu       | Load half word unsigned            | LHu Ra, [Rb+Cx]  |

| L       | SH        | Store half word                    | SH Ra, [Rb+Cx]   |

| L       | ADDiu     | Add immediate                      | ADDiu Ra, Rb, Cx |

| L       | ANDi      | AND imm                            | ANDi Ra, Rb, Cx  |

| L       | ORi       | OR                                 | ORi Ra, Rb, Cx   |

| L       | XORi      | XOR                                | XORi Ra, Rb, Cx  |

| L       | LUi       | Load upper                         | LUi Ra, Cx       |

| A       | CMP       | Compare                            | CMP Ra, Rb       |

| A       | ADDu      | Add unsigned                       | ADD Ra, Rb, Rc   |

| A       | SUBu      | Sub unsigned                       | SUB Ra, Rb, Rc   |

| A       | ADD       | Add                                | ADD Ra, Rb, Rc   |

| A       | SUB       | Subtract                           | SUB Ra, Rb, Rc   |

| A       | MUL       | Multiply                           | MUL Ra, Rb, Rc   |

| A       | AND       | Bitwise and                        | AND Ra, Rb, Rc   |

| A       | OR        | Bitwise or                         | OR Ra, Rb, Rc    |

| A       | XOR       | Bitwise exclusive or               | XOR Ra, Rb, Rc   |

| A       | ROL       | Rotate left                        | ROL Ra, Rb, Cx   |

| A       | ROR       | Rotate right                       | ROR Ra, Rb, Cx   |

| A       | SRA       | Shift right                        | SRA Ra, Rb, Cx   |

| A       | SHL       | Shift left                         | SHL Ra, Rb, Cx   |

| A       | SHR       | Shift right                        | SHR Ra, Rb, Cx   |

| A       | SRAV      | Shift right                        | SRAV Ra, Rb, Rc  |

| A       | SHLV      | Shift left                         | SHLV Ra, Rb, Rc  |

| A       | SHRV      | Shift right                        | SHRV Ra, Rb, Rc  |

| A       | ROL       | Rotate left                        | ROL Ra, Rb, Rc   |

| A       | ROR       | Rotate right                       | ROR Ra, Rb, Rc   |

| J       | JEQ       | Jump if equal (==)                 | JEQ Cx           |

| J       | JNE       | Jump if not equal (!=)             | JNE Cx           |

| J       | JLT       | Jump if less than (<)              | JLT Cx           |

| J       | JGT       | Jump if greater than (>)           | JGT Cx           |

| J       | JLE       | Jump if less than or equals $(<=)$ | JLE Cx           |

| J | JGE    | Jump if greater than or equals (>=) | JGE Cx           |

|---|--------|-------------------------------------|------------------|

| J | JMP    | Jump (unconditional)                | JMP Cx           |

| J | JALR   | Indirect jump                       | JALR Rb          |

| J | JSUB   | Jump to subroutine                  | JSUB Cx          |

| J | JR/RET | Return from subroutine              | JR \$1 or RET LR |

| A | MULT   | Multiply for 64 bits result         | MULT Ra, Rb      |

| A | MULTU  | MULT for unsigned 64 bits           | MULTU Ra, Rb     |

| A | DIV    | Divide                              | DIV Ra, Rb       |

| A | DIVU   | Divide unsigned                     | DIVU Ra, Rb      |

| A | MFHI   | Move HI to GPR                      | MFHI Ra          |

| A | MFLO   | Move LO to GPR                      | MFLO Ra          |

| A | MTHI   | Move GPR to HI                      | MTHI Ra          |

| A | MTLO   | Move GPR to LO                      | MTLO Ra          |

| A | MFC0   | Move C0R to GPR                     | MFC0 Ra, Rb      |

| A | MTC0   | Move GPR to C0R                     | MTC0 Ra, Rb      |

| A | C0MOV  | Move C0R to C0R                     | C0MOV Ra, Rb     |

Tabela 3.3: Instruções adicionadas no Cpu032II a partir do Cpu032I

| Formato | Mnemônico | Descrição           | Sintaxe          |

|---------|-----------|---------------------|------------------|

| L       | SLTi      | Set less Then       | SLTi Ra, Rb, Cx  |

| L       | SLTiu     | SLTi unsigned       | SLTiu Ra, Rb, Cx |

| A       | SLT       | Set less Then       | SLT Ra, Rb, Rc   |

| A       | SLTu      | SLT unsigned        | SLTu Ra, Rb, Rc  |

| L       | BEQ       | Branch if equal     | BEQ Ra, Rb, Cx   |

| L       | BNE       | Branch if not equal | BNE Ra, Rb, Cx   |

| J       | BAL       | Branch and link     | BAL Cx           |

### 3.2.4 O registrador de status (SW)

O registrador de status (SW) da Cpu0 contém o estado dos campos sinalizadores: Negative (N), Zero (Z), Carry (C), Overflow (V), Debug (D), Mode (M) e Interrupt (I). Sua configuração é ilustrada na Figura 3.6 a seguir.

Figura 3.6: Formato do registrador SW

Esses campos são modificados a partir da execução de determinadas instruções. Por exemplo,

ao executar a instrução CMP Ra, Rb, temos que:

- Se Ra > RB, então N = 0 e Z = 0.

- Se Ra < Rb, então N = 1 e Z = 0.

- Se Ra = Rb, então N = 0 e Z = 1.

São utilizados para, entre outras finalidades, determinar se um salto condicional será tomado ou não, identificar erros e falhas, acionar interrupções, etc.

#### 3.3 Caminho de dados

O Cpu0 é uma implementação pipeline de cinco estágios: fetch, instruction decode, execution, memory access e write-back.

No estágio *fetch*, a instrução é obtida pelo endereço de memória guardado no PC e é armazenada em IR. Após isso, PC é incrementado em quatro (uma vez que o endereçamento é dado em byte e o tamanho das instruções é de 32 bits.).

No estágio *instruction decode*, a unidade de controle do Cpu0 decodifica a instrução armazenada em IR, envia os valores dos registradores às entradas da ULA e configura o modo de operação da ULA baseado no campo opcode, bem como envia os sinais de controle para os próximos estágios.

No estágio *execute*, a ULA executa a operação determinada e armazena o resultado no registrador de destino, a menos que se trate de uma instrução que não seja lógico-aritmética.

No estágio *memory access*, quando for uma instrução LOAD, o dado da memória é armazenado no registrador MEM/WB. Quando for uma instrução STORE, o dado do registrador de origem é armazenado na memória.

No estágio *write-back*, usado apenas quando se tratar de uma instrução LOAD, o dado é repassado do registrador MEM/WB para o registrador de destino.

## Capítulo 4

## O Backend LLVM Cpu0

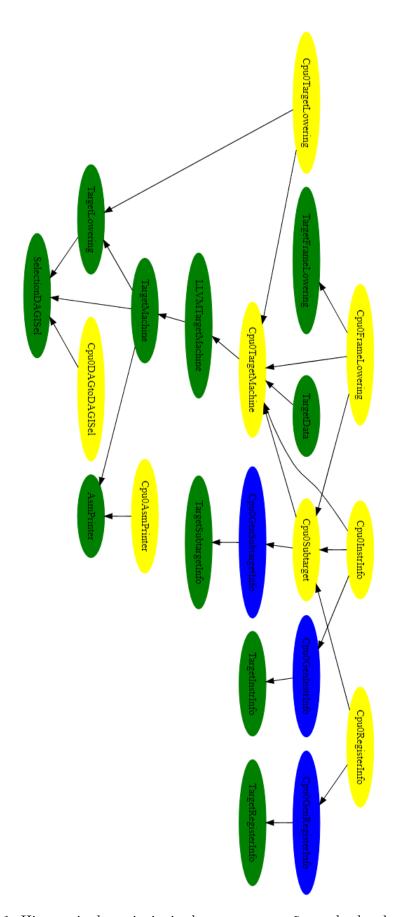

Este Capítulo apresenta o desenvolvimento do backend LLVM para o processador didático Cpu0, o qual foi realizado por Chen Chung-Shu [8]. No desenvolvimento, foi utilizado o framework de geração de código do LLVM - também chamado de "gerador de código" (é possível desenvolver um backend LLVM "do zero", no entanto é um processo bem mais dispendioso [16]). O gerador de código fornece uma hierarquia de classes base a partir das quais são implementadas subclasses que fornecem informações relativas às características e peculiaridades da máquina alvo. O framework também disponibiliza um conjunto de algoritmos - que são independentes de qualquer máquina alvo, e por isso podem ser utilizados para construção de geradores de código para uma variedade de processadores - que implementam fases da geração do código, como por exemplo: seleção de instruções, escalonamento de instruções e alocação de registradores, entre outras. Esses algoritmos fazem uso, portanto, das informações específicas da máquina para a qual se desenvolve o backend, de modo que o gerador de código funcione corretamente. A Figura 4.1 ilustra a hierarquia das principais classes implementadas. Em verde encontra-se as classes basilares fornecidas pelo gerador de código. Em amarelo encontra-se as classes implementadas manualmente para o backend Cpu0. Em azul encontram-se as classes geradas automaticamente pela ferramenta TableGen a partir dos arquivos de descrição.

Figura 4.1: Hierarquia das principais classes que compõem o backend do Cpu0.

A organização deste Capítulo é composta da seguinte forma: a Seção 4.1 apresenta os primeiros passos na construção do backend; as Seções 4.2 a 4.6 descrevem os trabalhos realizados para implementar as etapas mais relevantes da geração do código de máquina; por fim, a Seção 4.7 apresenta como o backend é integrado à estrutura do LLVM a fim de poder finalmente ser utilizado.

## 4.1 Informações gerais do backend

O primeiro passo na construção do backend LLVM para uma nova arquitetura é a implementação de uma subclasse da classe basilar *TargetMachine*. Essa classe é utilizada, entre outros fins, para que o gerador de código possa acessar os diversos componentes do backend utilizados no processo de geração de código, como o conjunto de instruções, banco de registradores, *stack frame*, etc. Além disso, ela define algumas características, como: o *layout* dos dados, tamanho do ponteiro, se é adotado *big endian* ou *little endian*. A classe Cpu0TargetMachine foi implementada para este fim (Figura 4.2). No caso do backend do Cpu0, o desenvolvedor do backend decidiu implementar essa interface no escopo da classe Cpu0Subtarget, como pode ser visto na Figura 4.3, onde definiu-se uma série de métodos que acessam os respectivos componentes. Caso algum módulo não faça referência à classe Subtarget, a mesma pode ainda ser acessada por meio da Cpu0TargetMachine a partir de um *static cast*.

```

Cpu0TargetMachine::Cpu0TargetMachine(const Target &T, const Triple &TT,

StringRef CPU, StringRef FS,

const TargetOptions &Options,

Optional<Reloc::Model> RM,

CodeModel::Model CM. CodeGenOpt::Level OL.

bool isLittle)

: LLVMTargetMachine(T, computeDataLayout(TT, CPU, Options, isLittle), TT,

CPU, FS, Options, getEffectiveRelocModel(CM, RM), CM,

OL),

isLittle(isLittle), TLOF(make_unique<Cpu0TargetObjectFile>()),

ABI (Cpu0ABIInfo::computeTargetABI()),

DefaultSubtarget(TT, CPU, FS, isLittle,

static std::string computeDataLayout(const Triple &TT,

StringRef CPU,

const TargetOptions &Options,

bool isLittle) {

std::string Ret = "";

if (isLittle)

Ret. += "e":

Ret += "-m:m-p:32:32-i8:8:32-i16:16:32-i64:64-n32-S64";

return Ret;

```

Figura 4.2: Implementação da classe CpuTargetMachine que integra o backend.

```

class Cpu0Subtarget : public Cpu0GenSubtargetInfo {

virtual void anchor();

public:

Cpu0Subtarget &initializeSubtargetDependencies(StringRef CPU, StringRef FS,

const TargetMachine &TM);

const SelectionDAGTargetInfo *getSelectionDAGInfo() const override {

return &TSInfo;

const Cpu0InstrInfo *getInstrInfo() const override { return InstrInfo.get(); }

const TargetFrameLowering *getFrameLowering() const override {

return FrameLowering.get();

const Cpu0RegisterInfo *getRegisterInfo() const override {

return &InstrInfo->getRegisterInfo();

const Cpu0TargetLowering *getTargetLowering() const override {

return TLInfo.get();

const InstrItineraryData *getInstrItineraryData() const override {

return &InstrItins;

1:

```

Figura 4.3: Implementação da classe CpuSubtarget que integra o backend.

## 4.2 Seleção de instruções

A seleção de instruções é a primeira etapa do processo de geração de código. Esta etapa é dividida em algumas fases, conforme visto no Capítulo 2, cujas implementações são demonstradas nas subseções abaixo. A Figura 4.4 retrata uma função em LLVM IR que será usada como exemplo para elucidar as transformações sofridas nos DAGs durante esta etapa. A função recebe dois números inteiros como parâmetros e retorna o módulo da subtração entre esses números.

```

define i32 @moduloDiferenca (i32 %n1, i32 %n2) nounwind {

inicio:

%tmp = sub nsw i32 %n1, %n2

%cmp = icmp sge i32 %tmp, 0

br i1 %cmp, label %then, label %else

then:

%result1 = sub nsw i32 %n1, %n2

ret i32 %result1;

else:

%result2 = sub nsw i32 %n2, %n1

ret i32 %result2;

}

```

Figura 4.4: Código LLVM IR da função moduloDiferenca utilizada como exemplo durante o processo de geração de código de máquina.

#### 4.2.1 Construção do DAG inicial

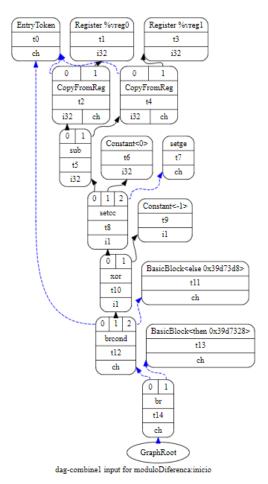

O código de entrada do backend, na representação intermediária LLVM, é, inicialmente, transformado em um grafo acíclico direcionado (DAG). As classes SelectionDAGBuild e TargetLowering do gerador de código são responsáveis pela construção do DAG inicial e, portanto, subclasses delas foram implementadas no backend do Cpu0. Para cada bloco de código LLVM é gerado um DAG (no caso da função da Figura 4.4, é gerado um DAG para o bloco "inicio", "then"e "else") e para cada instrução deste bloco é criado um nó do DAG, que são instâncias da classe SDNode. Cada nó possui um opcode, para identificar a operação, e seus operandos, caso houver. Cada nó define um ou mais valores aos quais são associados seus respectivos MVT (Machine Value Type), que indica o tipo de resultado. Há dois tipos de valores como resultado: os que representam dados propriamente dito (inteiros ou ponto flutuantes) e os que envolvem fluxo de controle, representados por ligações em cadeias que permitem definir a ordem entre os nós de efeitos secundários (como exemplo os loads, stores, calls, returns, etc). Os nós desse tipo recebem um token chain como entrada e geram um novo token chain como saída. No caso do bloco "inicio" da função da Figura 4.4, o DAG inicial gerado é:

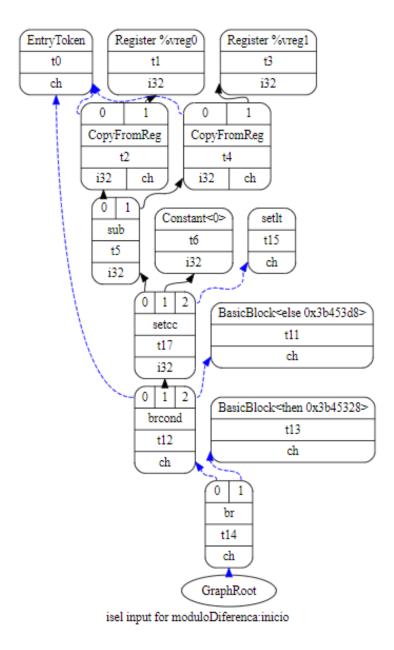

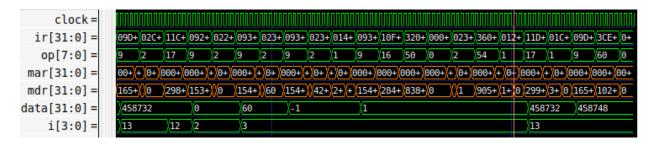

Figura 4.5: DAG inicial do bloco "inicio" da função modulo Diferenca.

Os valores dos parâmetros de entrada são copiados aos registradores t2 e t4. Nota-se que a

instrução **icmp** é transformada em **setcc**, que recebe o resultado da subtração, a constante 0 e a condição de comparação como parâmetros de entrada. A instrução **br** é transformada em **brcond** e recebe como parâmetros de entrada o **nó EntryToken**, o resultado de **setcc** invertido e o endereço de destino do salto caso **setcc** resulte logicamente em falso (ou seja, o endereço do bloco "else"). Por fim, o nó **br** recebe como parâmetro o nó brcond e t13 que contém o endereço de destino (bloco "then") caso **brcond** não tenha sido efetivado.

### 4.2.2 Otimização do DAG inicial

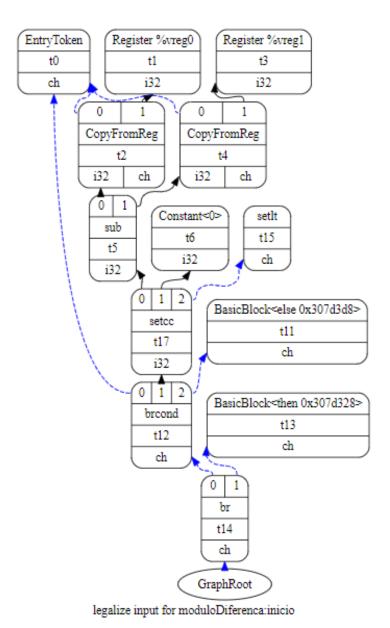

Antes da etapa de legalização do DAG, o gerador de código realiza um passo de otimização no DAG inicial a fim de tornar o código mais limpo, independente da máquina alvo. O DAG da Figura 4.5 é transformado no da Figura 4.6. Percebe-se que o tipo de comparação é alterado (de **setge** para **setlt**) de maneira que não é mais necessário o nó **XOR**.

Figura 4.6: DAG otimizado do bloco "inicio" da função modulo Diferenca.

#### 4.2.3 Legalização do DAG

A fase de legalização do DAG é a responsável por transformar o DAG, dando tratamento a todas as instruções e tipos de dados não suportados pela máquina alvo. É necessário, para tanto, fornecer ao gerador de código informações específicas da CPU, entre elas:

- Como expandir ou contrair instruções e/ou operandos a fim de que possam ser utilizadas pela CPU?

- Como tratar as instruções que não podem ser transformadas automaticamente?

- Quais são os tipos de dados suportados para cada instrução e, para cada um deles, a classe de registradores que deve ser utilizada?

- Como tratar as convenções de chamadas de função?

A classe TargetLowering é disponilizada para fornecer grande parte dessas informações ao gerador de código e, por isso, sua subclasse Cpu0TargetLowering foi implementada para este fim. As subseções abaixo apresentam suas principais implementações.

#### 4.2.3.1 Convenções de chamada

As convenções de chamada correspondem ao modo como argumentos e valores de retorno são repassados durante as chamadas de funções para uma determinada máquina-alvo. A depender da ABI (*Application Binary Interface*), um conjunto de restrições podem ou não ser exigido para seu correto funcionamento. No caso do Cpu0, a única restrição estabelecida é ilustrada na Figura 4.7, definida no arquivo TableGen "Cpu0CallingConv.td". Ela define que para os valores de retorno, quando de tamanho 32 bits, devem ser utilizados os registradores V0, V1, A0 e A1, nessa ordem de prioridade.

```

def RetCC_Cpu0EABI : CallingConv<[

// i32 are returned in registers V0, V1, A0, A1

CCIfType<[i32], CCAssignToReg<[V0, V1, A0, A1]>>

]>;

```

Figura 4.7: Convenções de chamada de função adotadas na construção do backend LLVM Cpu0.

A Cpu0TargetLowering é responsável por tratar cada chamada feita a uma função. Ao chamar uma função, entrar em seu escopo e retornar a execução, as seguintes funções são executadas, respectivamente:

LowerCall(): Quando uma função é chamada, antes é necessário passar todos os argumentos ao local apropriado. A função LowerCall() é a responsável por esta tarefa. Ela calcula, inicialmente, o quanto de memória é preciso e passa esse valor como um argumento da pseudo-instrução CALLSEQ\_START que insere uma sequência de **stores** para passar os argumentos à pilha. Em seguida, a instrução **call** é então inserida e, por fim, a pseudo-instrução CALLSEQ\_END, que indica ao *framework* o fim da sequência.

LowerFormalArguments(): Essa função é executada para garantir que o escopo da função chamada possa acessar os argumentos, o que significa estarem disponíveis em registradores virtuais. Aqueles que já estão em registradores são simplesmente copiados para os registradores virtuais. Aqueles que estão na pilha são carregados para os registradores virtuais através da inserção de instruções load.

LowerReturn(): Ao sair do escopo da função chamada, a função LowerReturn() é invocada.O valor de retorno, caso exista, é passado a algum registrador físico conforme as convenções de chamada e um nó RET\_FLAG é inserido no DAG para que, na fase de seleção de instrução, seja substituído pela instrução nativa de retorno **ret**.

#### 4.2.3.2 Transformação manual de instruções ilegais

Geralmente, há instruções e/ou operandos que precisam ser transformadas manualmente devido a certas propriedades e restrições do microprocessador. A implementação dessas transformações se dá tanto em arquivos de descrição TableGen quanto em códigos em C++. Classes customizadas da SDNode são primeiramente definidas em Cpu0InstrInfo.td e as operações são especificadas no construtor da Cpu0TargetLowering. Nesta etapa substituí-se os nós em questão por outros nós intermediários que possam ser utilizados na etapa de seleção de instrução. Entre as transformações mais comuns realizadas nos backends LLVM estão as adequações para instruções de saltos condicionais e de shit de bits, pois muitas vezes a arquitetura não possui um registrador com flags de comparação nem instruções de shift que possam ser transformadas automaticamente a partir das instruções contidas na LLVM IR.

No caso do Cpu0, entre as poucas transformações manuais realizadas tem-se as que dizem respeito a endereços virtuais absolutos, como no caso de *Global Adresses*. Basicamente o endereço é dividido em duas partes - Hi e Lo - e um nó ADD é inserido para somar essas partes (conforme Figura 4.8), possibilitando ao seletor de instruções posteriormente converte essa adição em um endereço de memória utilizado pelas instruções de acesso a memória.

```

SDValue Cpu0TargetLowering::

lowerGlobalTLSAddress(SDValue Op, SelectionDAG &DAG) const

{

...

SDValue TGAHi = DAG.getTargetGlobalAddress(GV, DL, PtrVT, 0,

Cpu0II::MO_DTP_HI);

SDValue Hi = DAG.getNode(Cpu0ISD::Hi, DL, PtrVT, TGAHi);

SDValue TGALo = DAG.getTargetGlobalAddress(GV, DL, PtrVT, 0,

Cpu0II::MO_DTP_LO);

SDValue Lo = DAG.getNode(Cpu0ISD::Lo, DL, PtrVT, TGALo);

SDValue Add = DAG.getNode(ISD::ADD, DL, PtrVT, Hi, Ret);

return DAG.getNode(ISD::ADD, DL, PtrVT, Add, Lo);

...

```

Figura 4.8: Trecho de código da Cpu0TargetLowering que trata a transformação manual de GlobalAdresses.

O DAG ilegal da Figura 4.6 é então transformado no DAG legalizado da Figura 4.9.

Figura 4.9: DAG legalizado do bloco "inicio" da função modulo Diferenca.

### 4.2.4 Seleção de instruções

Uma vez que o DAG esteja legalizado, ele deve passar por uma última transformação, onde seus nós são transformados em instruções que são suportadas pelo Cpu0 de forma nativa. Para isso, o gerador de código necessita de informações detalhadas a respeito do conjunto de instruções do Cpu0. Conforme visto no Capítulo 2, a TableGen exerce esse papel. Os arquivos Cpu0InstrFormats.td e Cpu0InstrInfo.td contém a descrição dos formatos das instruções e suas definições de fato, respectivamente.

#### 4.2.4.1 Descrição do formato de instruções

As instruções devem ser especificadas a partir da classe Instruction. A classe Cpu0Inst foi implementada como uma subclasse daquela e é utilizada na implementação das classes que especificam os formatos de instruções do Cpu0. Conforme a Figura 4.10, o opcode é definido como os oito bits mais significativos da instrução, uma vez que seu tamanho e posição são os mesmos para todos os formatos de instruções, conforme visto no Capítulo 3. Além disso, é possível definir quantos operandos a instrução tem, seus respectivos tamanhos e mapeamento no código da instrução.

```

// Generic Cpu0 Format

class Cpu0Inst<dag outs, dag ins, string asmstr, list<dag> pattern,

InstrItinClass itin, Format f>: Instruction

field bits<32> Inst;

Format Form = f:

let Namespace = "Cpu0";

let Size = 4;

bits<8> Opcode = 0;

let Inst{31-24} = Opcode;

let OutOperandList = outs;

let InOperandList = ins;

let AsmString = asmstr;

= pattern;

let Pattern

let Itinerary = itin;

bits<4> FormBits = Form.Value;

let TSFlags{3-0} = FormBits;

let DecoderNamespace = "Cpu0";

field bits<32> SoftFail = 0;

```

Figura 4.10: Implementação da classe de instruções genérica dentro do escopo da TableGen.

Para as instruções do formato A, a classe FA foi implementada. os operandos **ra**, **rb**, **rc** e **o shamt** são definidos a partir dos bits da instrução, conforme Figura 4.11.

Figura 4.11: Implementação da classe de formato de instruções do tipo A dentro do escopo da TableGen.

De semelhante modo, as classes FL e FJ foram implementadas para as instruções de formato

L e J, respectivamente, conforme suas particularidades apresentadas no Capítulo 3:

Figura 4.12: Implementação da classe de formato de instruções do tipo L dentro do escopo da TableGen.

Figura 4.13: Implementação da classe de formato de instruções do tipo J dentro do escopo da TableGen.

#### 4.2.4.2 Descrição do conjunto de instruções

A partir das descrições de formatos fornecidas anteriormente, as instruções podem ser descritas detalhadamente. Para fins de exemplo, iremos demonstrar a definição das instruções ADD e ORi para explicar o processo de descrição de uma instrução, que é realizado para cada uma das instruções do processador. Essas operações realizam, respectivamente:

- 1.  $Ra \le Rb + Rc$

- 2. Ra  $\leq$  Rb OR Cx

As Figuras 4.14 e 4.15 ilustram seus formatos, respectivamente:

| 8 bits  | 4 bits | 4 bits | 4 bits | 12 bits     |  |

|---------|--------|--------|--------|-------------|--|

| 0x13    | Ra     | Rb     | Rc     | Cx (12bits) |  |

| MSB LSB |        |        |        |             |  |

Figura 4.14: Formato da instrução ADD.

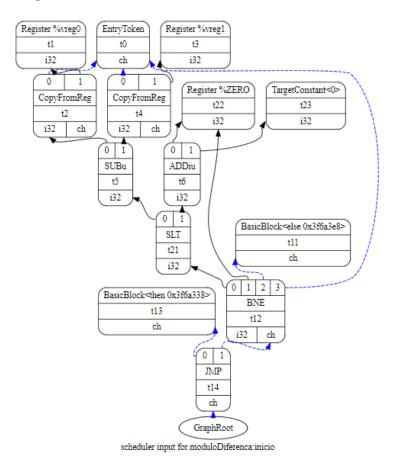

Figura 4.15: Formato da instrução ORi.

Primeiramente, é preciso descrever os operandos das instruções. Muitos operandos já estão pre-definidos na TableGen, no entanto, há situações onde isso não é suficiente. No caso do ADD, os operandos Ra, Rb e Rc são todos registradores e são descritos em CpuRegisterInfo.td (conforme a seção 4.4), sendo assim, pode-se definir diretamente a instrução:

```

def ADD : ArithLogicR<0x13, "add", add, IIAlu, CPURegs, 1>;

```

Figura 4.16: Definição da instrução ADD dentro do escopo da TableGen.

Os parâmetros passados são o opcode (0x13), a string da instrução ("add"), o opNode (add), que é o tipo de SDNode usado como pattern no momento de seleção da instrução, o tipo de itinerário (IIAlu), que será usado no escalonamento de instruções, a classe de registradores dos operandos(CPURegs) e a flag isComutable (1), que define se a operação em questão é ou não comutativa. Nota-se que a ADD é definida a partir da classe ArithLogicR. Tal classe foi implementada a partir da classe FA (apresentada na seção anterior) e agrega informações comuns às operações lógico-aritméticas cujos operandos sejam somente registradores. Os operandos de entrada e saída assumem o formato "local:\$nome", onde 'local' é uma classe de registradores ou uma instância (pre-definida ou customizada) de Operand (classe interna da TableGen) e \$nome é usado pelo AsmPrinter no processo de emissão de código. Além disso, a linha 5 da Figura 4.17 descreve o pattern que permite o gerador de código selecionar a instrução de máquina corretamente a partir do código LLVM IR.

```

class ArithLogicR<br/>lits<br/>| InstrItinClass itin, RegisterClass RC, bit isComm = 0>:<br/>FA<op, (outs GPROut:$ra), (ins RC:$rb, RC:$rc),<br/>!strconcat(instr_asm, "\t$ra, $rb, $rc"),<br/>[(set GPROut:$ra, (OpNode RC:$rb, RC:$rc))], itin> {<br/>let shamt = 0;<br/>let isCommutable = isComm; // e.g. add rb rc = add rc rb<br/>let isReMaterializable = 1;

```

Figura 4.17: Implementação da classe ArithLogicR, classe utilizada para definir as instruções logicas e aritméticas cujos operandos são somente registradores.

No caso do ORi, define-se o operando imediato da forma a seguir (isso é feito para qualquer instrução que utilize operandos especiais, como por exemplo as instruções de saltos, que possuem endereço de destino com tamanho de 24 bits.). O imediato é definido como uma instância da classe interna da TableGen *Operand*, onde informa-se à TableGen o nome do método da classe AsmPrinter responsável pela sua emissão em assembly (na fase de emissão de código).

Assim, define-se a instrução:

```

def uimm16 : Operand<i32> {

let PrintMethod = "printUnsignedImm";

}

```

Figura 4.18: Definição do operando imediato utilizado pela instrução ORi.

```

def ORi : ArithLogicI<0x0d, "ori", or, uimml6, immZExtl6, CPURegs>;

```

Figura 4.19: Definição da instrução ORi dentro do escopo da TableGen.

Nesse caso, uma nova classe base é utilizada, a ArithLogicI, que é definida a partir da classe FL (uma vez que a instrução ORi é do formato L):

Figura 4.20: Implementação da classe ArithLogicI, classe utilizada para definir as instruções logicas e aritméticas cujos operandos são registradores e valores imediatos.

#### 4.2.4.3 O seletor de instruções

Uma vez que todas as instruções foram definidas, é possível realizar efetivamente a seleção de instrução de máquina para cada um dos nó do DAG legalizado, transformando-o em um DAG de instruções da máquina alvo. Isso é feito por meio da correspondência entre os nós do DAG e os respectivos patterns das instruções, conforme a sequência de etapas a seguir:

- 1) O gerador de código executa o método SelectionDagISel::DoInstructionSelection que é responsável por invocar o seletor de instruções conforme o target utilizado. No caso, o método Cpu0DAGToDAGISel::Select é invocado para analisar e executar a seleção de instrução para cada nó do DAG legalizado.

- 2) Caso houvesse correspondências de instruções a serem feitas de forma manual, o método Cpu0ISelDagToDag::Select as realizaria e, posteriormente, invocaria o método responsável pelas correspondências automáticas. No caso do Cpu0, nenhuma correspondência manual é necessária, de modo que o método CpuDagToDagISel::SelectCode é invocado para realizar as correspondências automáticas. Este método é gerado automaticamente a partir dos arquivos de descrição TableGen das instruções, descritos acima.

- 3) O Cpu0ISelDagToDag::SelectCode faz, para cada um dos nós do DAG em transformação, uma varredura entre as instruções buscando a correspondência correta. Pode ser que haja mais de uma instrução cujo *pattern* corresponda adequadamente ao nó. Nesses casos, a primeira correspondência encontrada é utilizada.

#### 4.2.4.4 Informações não estáticas

Além das descrições fornecidas a partir da ferramenta TableGen, é necessário implementar alguns métodos que analisam, inserem e transformam algumas instruções. Esses métodos são convocados na etapa final da geração de código e realizam, por exemplo, análises de saltos (inserindo-os ou removendo-os, conforme o caso), manipulações de registradores para uma utilização eficiente dos mesmos, etc.

Assim, o DAG final da etapa de seleção de instruções é mostrado na Figura 4.21, transformado a partir do DAG da Figura 4.9:

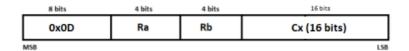

Figura 4.21: DAG final do bloco "inicio" da função modulo Diferenca.

### 4.3 Escalonamento de Instruções

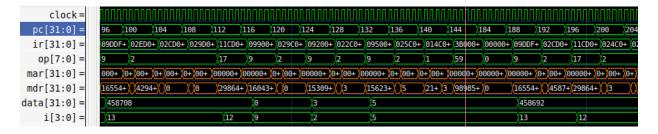

O escalonamento de instruções é a fase em que o DAG legalizado é transformado em uma lista de instruções, que são representadas por instâncias da classe MachineInstr. Essa transformação é feita buscando minimizar a latência do processador e otimizar o uso dos registradores. O LLVM faz uso de informações como quais são as unidades funcionais do processador, quais delas são utilizadas por cada instrução, suas latências, etc., para se ter um bom escalonamento. Após a geração da lista, o DAG é destruído. No caso do Cpu0, o desenvolvedor do backend decidiu

não fornecer muitos detalhes desses aspectos da arquitetura. A lista de instruções geradas pelo escalonador a partir do DAG da Figura 4.21 é:

```

BB#0: derived from LLVM BB %inicio

Live Ins: %A0 %A1

%vregl<def> = COPY %A1; CPURegs:%vregl

%vreg0<def> = COPY %A0; CPURegs:%vreg0

%vreg2<def> = SUBu %vreg0, %vreg1; GPROut:%vreg2 CPURegs:%vreg0,%vreg1

%vreg3<def> = ADDiu %ZERO, 0; GPROut:%vreg3

%vreg4<def> = SLT %vreg2, %vreg3; GPROut:%vreg4,%vreg2,%vreg3

BNE %vreg4, %ZERO, <BB#2>, %AT<imp-def,dead>; GPROut:%vreg4

JMP <BB#1>

```

Figura 4.22: Código gerado a partir do bloco "inicio" da função modulo Diferenca após etapa "Escalonamento de Instruções".

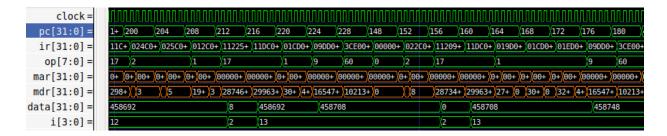

### 4.4 Alocação dos registradores

Nesta etapa, o gerador de código realiza a alocação dos registradores. Para isso, é necessário descrever detalhadamente o banco de registradores ao LLVM. A maior parte das informações são fornecidas por meio da TableGen. No entanto, como será visto, algumas informações dependem de fatores não conhecidos antes da execução, e precisam ser implementadas separadamente em códigos C++.

#### 4.4.0.1 Descrição do banco de registradores

A partir da classe Register fornecida pela TableGen foram implementadas as classes de registradores do Cpu0.

```

class Cpu0Reg<bits<16> Enc, string n> : Register<n> {

let HWEncoding = Enc;

let Namespace = "Cpu0";

}

class Cpu0GPRReg<bits<16> Enc, string n> : Cpu0Reg<Enc, n>;

class Cpu0COReg<bits<16> Enc, string n> : Cpu0Reg<Enc, n>;

```

Figura 4.23: Implementação da classe Cpu0Reg utilizada para definir os registradores do Cpu0 dentro do escopo da TableGen.

A classe Cpu0Reg define genericamente os registradores do Cpu0. A classe Cpu0GPRReg foi implementada para definir os registradores de uso geral e a classe Cpu0COReg define os registradores de uso específico ao processador, conforme a Figura 4.24. Cada registrador deve ser definido como uma instância de uma das classes acima. O número identificador e o nome do registrador são passados como argumentos. Ainda, o campo DWARF é definido para fins de depuração.

```

def ZERO : Cpu0GPRReg<0,</pre>

"zero">, DwarfRegNum<[0]>;

def AT : Cpu0GPRReg<1,</pre>

"1">, DwarfRegNum<[1]>;

"2">,

def V0

: Cpu0GPRReg<2,

DwarfRegNum<[2]>;

def V1 : Cpu0GPRReg<3, "3">, DwarfRegNum<[3]>;

"4">, DwarfRegNum<[4]>;

"5">, DwarfRegNum<[5]>;

def A0 : Cpu0GPRReg<4,</pre>

def A1 : Cpu0GPRReg<5,</pre>

def T9 : Cpu0GPRReg<6,</pre>

"t9">, DwarfRegNum<[6]>;

"7">,

def TO

: CpuOGPRReg<7,

DwarfRegNum<[7]>;

"8">,

def T1 : Cpu0GPRReg<8,

DwarfRegNum<[8]>;

def S0 : CpuOGPRReg<9, "9">, DwarfRegNum<[9]>;

: CpuOGPRReg<10, "10">, DwarfRegNum<[10]>;

def S1

def GP : Cpu0GPRReg<11, "gp">, DwarfRegNum<[11]>;

def FP : Cpu0GPRReg<12, "fp">, DwarfRegNum<[12]>;

def SP : Cpu0GPRReg<13, "gp">,

DwarfRegNum<[13]>;

def LR : Cpu0GPRReg<14, "lx">,

DwarfRegNum<[14]>;

def SW : CpuOGPRReg<15, "SW">,

DwarfRegNum<[15]>;

def HI : Cpu0Reg<0, "ac0">, DwarfRegNum<[18]>;

def LO : Cpu0Reg<0, "ac0">, DwarfRegNum<[19]>;

def PC

: Cpu0C0Reg<0, "pc">, DwarfRegNum<[20]>;