$$\begin{split} & \text{Universidade de Brasília} - \text{UnB} \\ & \text{Faculdade UnB Gama} - \text{FGA} \\ & \text{Engenharia Eletrônica} \end{split}$$

# PROJETO DO MODULADOR A/D DO TIPO $\Sigma\Delta$ DE BAIXO CONSUMO DE POTÊNCIA APLICADO EM MARCA PASSO

Autor: Karine Ribeiro dos Santos

Orientador: Prof. Dr. Sandro Augusto Pavlik Haddad

Brasília, DF 2017

#### Karine Ribeiro dos Santos

# PROJETO DO MODULADOR A/D DO TIPO ∑△ DE BAIXO CONSUMO DE POTÊNCIA APLICADO EM MARCA PASSO

Monografia submetida ao curso de graduação em Engenharia Eletrônica da Universidade de Brasília, como requisito parcial para obtenção do Título de Bacharel em Engenharia Eletrônica.

Universidade de Brasília – UnB Faculdade UnB Gama – FGA

Orientador: Prof. Dr. Sandro Augusto Pavlik Haddad

Brasília, DF 2017

Karine Ribeiro dos Santos

PROJETO DO MODULADOR A/D DO TIPO  $\Sigma\Delta$  DE BAIXO CONSUMO DE POTÊNCIA APLICADO EM MARCA PASSO/ Karine Ribeiro dos Santos. – Brasília, DF, 2017-

99 p. : il. (algumas color.) ; 30 cm.

Orientador: Prof. Dr. Sandro Augusto Pavlik Haddad

Trabalho de Conclusão de Curso – Universidade de Brasília – Un<br/>B Faculdade Un<br/>B Gama – FGA , 2017.

1. Palavra-chave<br/>01. 2. Palavra-chave<br/>02. I. Prof. Dr. Sandro Augusto Pavlik Haddad. II. Universidade de Brasília. III. Faculdade Un<br/>B Gama. IV. PROJETO DO MODULADOR A/D DO TIPO  $\Sigma\Delta$  DE BAIXO CONSUMO DE POTÊNCIA APLICADO EM MARCA PASSO

$CDU\ 02{:}141{:}005.6$

#### Karine Ribeiro dos Santos

# PROJETO DO MODULADOR A/D DO TIPO $\Sigma\Delta$ DE BAIXO CONSUMO DE POTÊNCIA APLICADO EM MARCA PASSO

Monografia submetida ao curso de graduação em Engenharia Eletrônica da Universidade de Brasília, como requisito parcial para obtenção do Título de Bacharel em Engenharia Eletrônica.

Trabalho apresentado e aprovado na data 08 de Setembro de 2017, em Brasília, DF, pela banca examinadora:

Prof. Dr. Sandro Augusto Pavlik Haddad

Orientador

Prof. Dr. Wellington Avelino do Amaral Convidado 1

Me. Yuri Cesar Rosa de Toledo Convidado 2

> Brasília, DF 2017

## Agradecimentos

Agradeço, primeiramente, à Deus por me conceder força, perseverança e fé para galgar os mais diversos caminhos e por nunca me deixar perder as oportunidades do bem. Ao meu pai, que me apoiaria em qualquer escolha que eu pudesse fazer ao longo da minha vida. A minha mãe, pelo amor gigantesco, lanchinhos da madrugada, abraços de incentivo e apoio ilimitado para realização do meu curso de graduação. Ao professor e orientador Sandro Haddad, pela orientação, críticas construtivas, paciência, apoio, confiança e oportunidade. A minha tia Anaurise, pela disponibilidade e boa vontade em me ajudar. A minha irmã Aline pela paciência e ajuda emocional. A Josefina pelas traduções. Ao meu namorado Guilherme pelas traduções, digitações, chocolates, críticas construtívas, incentivos constantes, apoio e paciência incondicional. Ao Yuri pelas ideias, disposição e paciência para me ensinar. A todos os meus amigos que me apoiam e acreditam em mim. Ao meu amigo Thiago pela ajuda com a construção dos desenhos, por todo carinho e paciência. E agradeço a todos que mesmo sem saber, fizeram os meus dias mais felizes durante o período de formação na faculdade.

## Resumo

O presente trabalho de conclusão de curso aborda o uso do conversor analógico digital do tipo Sigma Delta com baixo consumo de potência para aplicação em um aparelho de marca-passo utilizando a metodologia Top-Down. Para a escolha do tipo de conversor realizou-se comparações entre diversas topologias com relação à resolução, velocidade suficiente e baixo consumo de potência. A topologia adotada retrata a análise do conversor Sigma Delta e a determinação dos seus parâmetros. Detalhando o conversor escolhido, determinou-se parâmetros específicos como ENOB e SNR, e analisou-se, para fins de validação da escolha do sistema, as simulações de moduladores de primeira e segunda ordem apresentando a sua função de transferência, o lugar geométrico das raízes, diagrama de blocos e, por fim, análise gráfica da resposta utilizando o software MATLAB. Contemplase em nível transístor o modulador de primeira ordem e suas respectivas análises em AC, DC e transiente. Implementa-se, em baixo nível, uma proposta inovadora para o integrador do modulador de primeira ordem aplicando-se apenas um capacitor. Apresenta, também, a contextualização do projeto de um marca-passo, e a validação da simulação a partir da ferramenta CADENCE com tecnologia TSMC  $0.13\mu m$  utilizando circuitos CMOS translineares em modo corrente para os moduladores do conversor Sigma Delta.

Palavras-chaves: Microeletrônica. Conversor A/D. Conversor Sigma Delta. Baixo Consumo de Potência. Marca-passo.

### **Abstract**

This final undergraduate paper addresses the use of the low power consumption Sigma Delta analog-digital converter in pacemaker devices using a top-down approach. Comparisons between various topologies regarding resolution, sufficient speed and low power consumption lead to the selected converter. The adopted topology portrays the Sigma Delta converter analysis and the determination of its parameters. By detailing the converter, it was possible to determine specific parameters, such as ENOB and SNR; analyze the first and second order modulators' simulations, presenting their transference function, locus root, block diagram; including, finally, a graphical analysis of the answer using MATLAB software to validate the choice of the system. A transistor level analysis of the first order modulator's AC, DC, and transient. An innovative proposal for the first order modulator integrator here implemented at a low level employs only one capacitor. It also establishes context for a pacemaker's project and the simulation's validation derives out of the CADENCE tool with TSMC technology  $0.13\mu$ m using translinear CMOS circuits in current mode for the Sigma Delta converter modulators.

**Key-words**: Microelectronics. A/D converter. Sigma Delta Converter. Low Power Consumption. Pacemaker.

# Lista de ilustrações

| Figura 1 –  | Metodologia <i>Top/Down</i> para a implementação do conversor ADC Sigma  – Delta. (1) | 30 |

|-------------|---------------------------------------------------------------------------------------|----|

| Figura 2 -  | Exemplos de sinais (a) Analógico e contínuo no tempo, (b) Digital e                   |    |

| O           | contínuo no tempo, (c) Analógico e discreto no tempo. (d) Digital e                   |    |

|             | discreto no tempo. (2)                                                                | 36 |

| Figura 3 -  | Representação geral de um bloco de conversão A/D.(3)                                  | 37 |

|             | Descrição de forma sucinta e genérica de um conversor A/D. (4)                        | 37 |

|             | Modelo básico de Conversor <i>Two Step.</i> (5)                                       | 38 |

| _           | Topologia de conversor A/D tipo FLASH. (6)                                            | 39 |

|             | Topologia de conversor por aproximação sucessiva SAR. (7)                             | 40 |

| _           | Modulação do tipo Sigma-Delta (4)                                                     | 41 |

|             | Comparação entre parâmetros de um conversor ADC (8)                                   | 42 |

| _           | (a) Exemplo da entrada de um sinal (b) Espectro do sinal amostrado.                   |    |

|             | (9)                                                                                   | 43 |

| Figura 11 – | Características ideais de entrada e saída de uma DAC de 3-bits. (6)                   | 44 |

| Figura 12 – | Dente de serra com valor de 1LSB pico a pico em uma DAC de 3-bits.                    |    |

|             | (6)                                                                                   | 44 |

| Figura 13 – | INL, DNL, Monotonicidade em um DAC de 3 bit. (6)                                      | 45 |

|             | Coração humano: aspecto interno. (10)                                                 | 47 |

| Figura 15 – | Coração humano: aspecto externo. (10)                                                 | 48 |

| Figura 16 – | Visualização de um marca-passo e implantação do dispositivo no corpo                  |    |

|             | humano. (11)                                                                          | 49 |

| Figura 17 – | Visualização do CAD explodido de um marca-passo. (11)                                 | 50 |

| Figura 18 – | Formato de onda de um sinal de ECG                                                    | 50 |

| Figura 19 – | Diagrama de blocos de um $\Sigma\Delta$ . (12)                                        | 51 |

| Figura 20 – | Arquitetura do conversor $\Sigma\Delta$ (4)                                           | 52 |

| Figura 21 – | Ordem do Modulador $\Sigma\Delta$ e SNR x Taxa de amostragem (13)                     | 53 |

| Figura 22 – | Comportamento das Funções de Transferência no modulador $\Sigma\Delta$ uti-           |    |

|             | lizando um filtro passa-baixas                                                        | 53 |

| Figura 23 – | Comportamento das Funções de Transferência no modulador $\Sigma\Delta$ uti-           |    |

|             | lizando um filtro passa-altas.                                                        | 54 |

| Figura 24 – | Diagrama de Blocos de um modulador $\Sigma\Delta$ de $1^a$ ordem no domínio           |    |

|             | discreto (4)                                                                          | 55 |

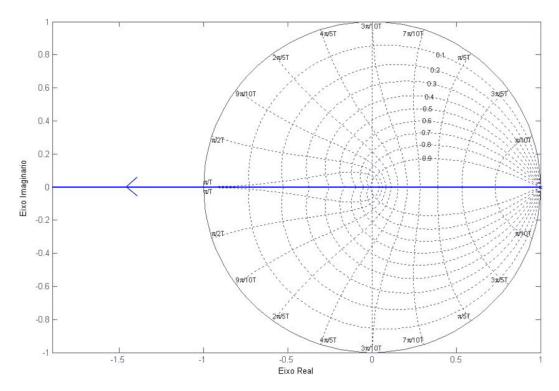

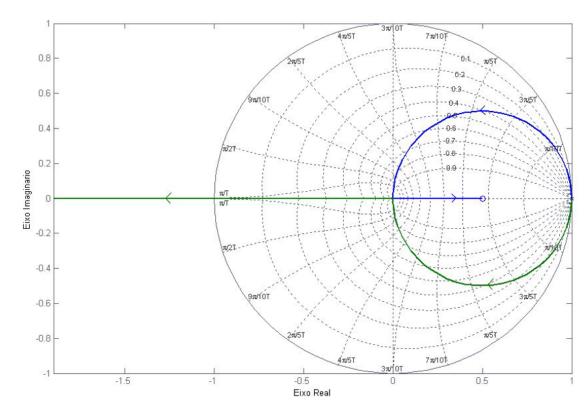

| Figura 25 – | Plotagem de LGR de 1ª ordem feita no software MATLAB com base                         |    |

|             | teórica em FÁVERO(14)                                                                 | 56 |

| Figura 26 – | Diagrama de blocos de um modulador Sigma-Delta de 1ª ordem                            | 56 |

| Figura 27 –   | Resposta modulador Sigma-Delta de 1ª ordem, com formas de ondas de sinal de (a) entrada, (b) diferenciador, (c) integrador, (d) quantizador, e (e) DAC.                                                                                                                         | 57       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figura 28 –   | Diagrama de Blocos de um modulador $\Sigma\Delta$ de 2ª ordem no domínio discreto (5)                                                                                                                                                                                           | 58       |

| Figura 29 –   | Plotagem de LGR de 2 <sup>a</sup> ordem feita no software MATLAB com base teórica em FÁVERO(14)                                                                                                                                                                                 | 59       |

|               | Diagrama de blocos de um modulador Sigma-Delta de 2ª ordem Resposta modulador Sigma-Delta de 2ª ordem, com formas de ondas de sinal de entrada (a), diferenciador do 1º ganho (b), 1º integrador (c), diferenciador após o 2º ganho (d), 2º integrador (e) e o quantizador (f). | 59<br>60 |

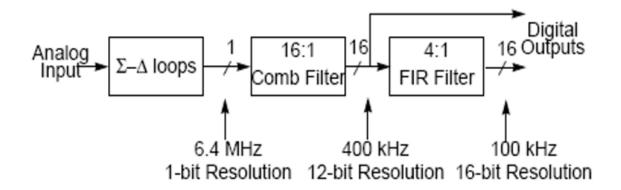

| Figura 32 –   | Etapa digital: filtragem e decimação (15)                                                                                                                                                                                                                                       | 61       |

|               | Processo de decimação digital (13)                                                                                                                                                                                                                                              | 62       |

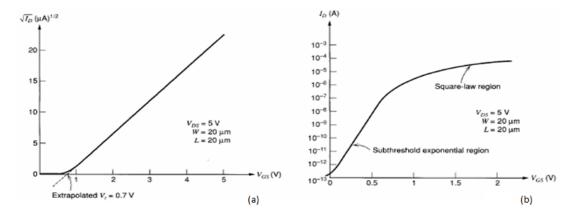

|               | Representação de um NMOS: (a) em região ativa plotada em escala linear demonstrando assim a lei quadrática; (b) em região de sub-limiar                                                                                                                                         |          |

|               | plotada em escala logarítmica demonstrando assim a lei exponencial                                                                                                                                                                                                              | 66       |

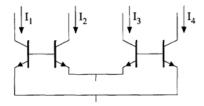

| _             | Representação do sentido da corrente em loop STL. (16)                                                                                                                                                                                                                          | 67       |

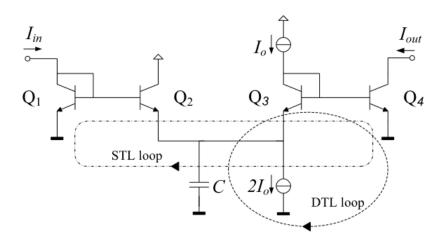

| Figura 36 –   | Representação DTL em transistores para validação. (17)                                                                                                                                                                                                                          | 68       |

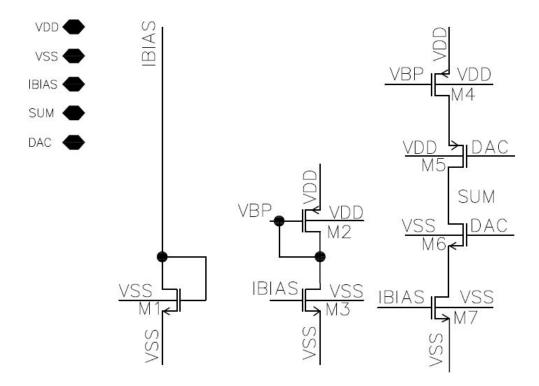

|               | Representação básica do bloco de um modulador de 1ª ordem                                                                                                                                                                                                                       | 71       |

| Figura 38 –   | Representação do modulador de 1ª ordem Corrente-Corrente                                                                                                                                                                                                                        | 71       |

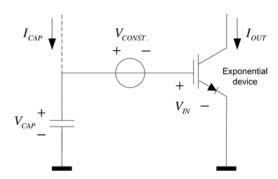

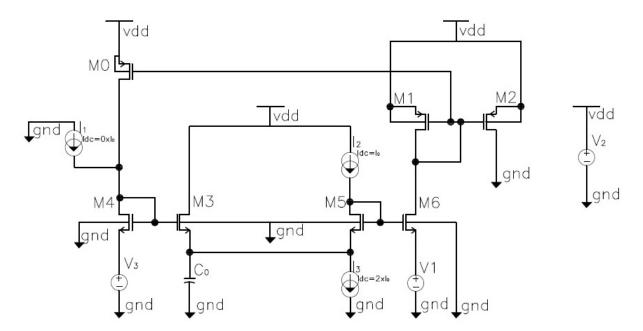

| Figura 39 –   | Representação simplificada de um integrador <i>Log-Domain</i> . (16)                                                                                                                                                                                                            | 72       |

| Figura 40 -   | Diagrama de bloco do filtro passa baixa de 1ª ordem em <i>Log-Domain</i> .                                                                                                                                                                                                      |          |

|               | $(16) \ldots \ldots$                                                                                                                                     | 72       |

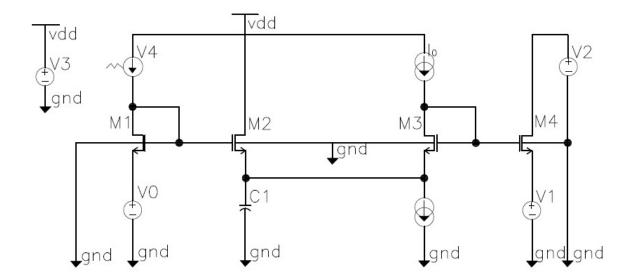

| Figura 41 –   | Topologia do filtro passa baixa de primeira ordem em <i>Log-Domain</i> . (17)                                                                                                                                                                                                   | 73       |

| Figura 42 –   | Implementação do filtro passa baixa de primeira ordem em $Log\text{-}Domain$                                                                                                                                                                                                    | 74       |

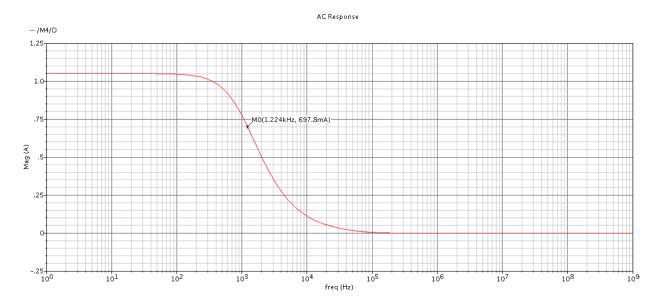

| Figura 43 -   | Análise AC do filtro de 1ª ordem                                                                                                                                                                                                                                                | 75       |

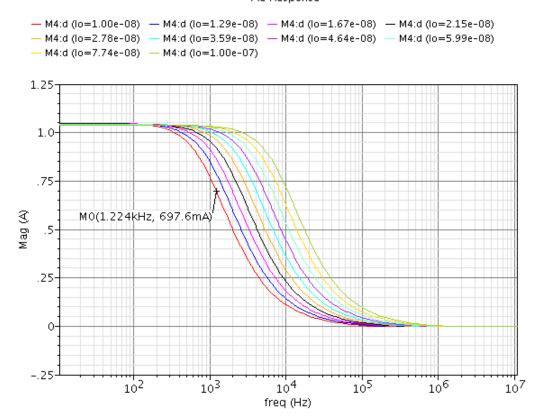

| Figura 44 -   | Análise em <i>Parametric Analyses</i> para verificação quanto a alterações                                                                                                                                                                                                      |          |

|               | da corrente no filtro                                                                                                                                                                                                                                                           | 76       |

| Figura 45 -   | Análise Transiente com sinal de ECG aplicado ao filtro passa baixas                                                                                                                                                                                                             |          |

|               | proposto                                                                                                                                                                                                                                                                        | 77       |

| Figura 46 –   | Implementação do Integrador em $Log\text{-}Domain$                                                                                                                                                                                                                              | 77       |

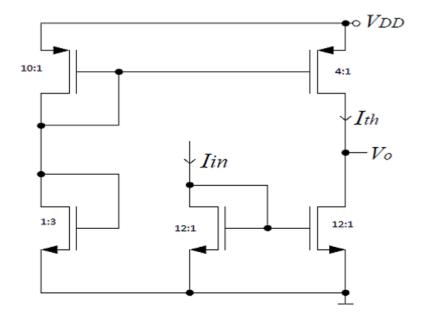

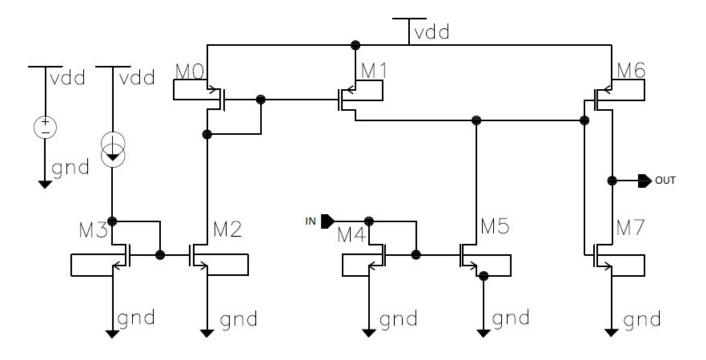

| Figura 47 –   | Topologia básica da implementação do circuito comparador de corrente (10)                                                                                                                                                                                                       | 78       |

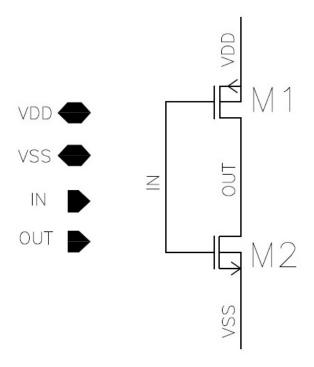

| Figure 12     | Implementação do circuito inversor                                                                                                                                                                                                                                              | 79       |

|               | Símbolo do Esquemático do circuito inversor                                                                                                                                                                                                                                     | 79       |

|               |                                                                                                                                                                                                                                                                                 | 80       |

|               | Implementação do circuito comparador de corrente                                                                                                                                                                                                                                |          |

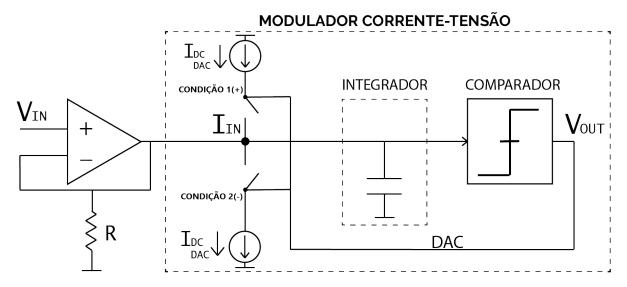

|               | Representação do modulador de 1ª ordem corrente-tensão                                                                                                                                                                                                                          | 81       |

|               | Representação simbólica de um capacitor                                                                                                                                                                                                                                         | 81<br>82 |

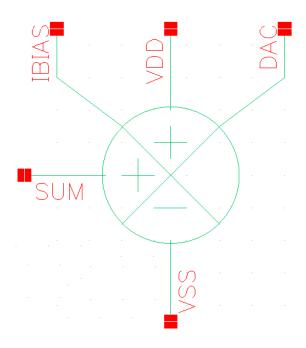

| + 1911ra 53 - | · Sumbolo do circulto DAC                                                                                                                                                                                                                                                       | 87.      |

| Figura 54 – Esquemático do DAC do modulador de 1ª ordem 8                       | 33 |

|---------------------------------------------------------------------------------|----|

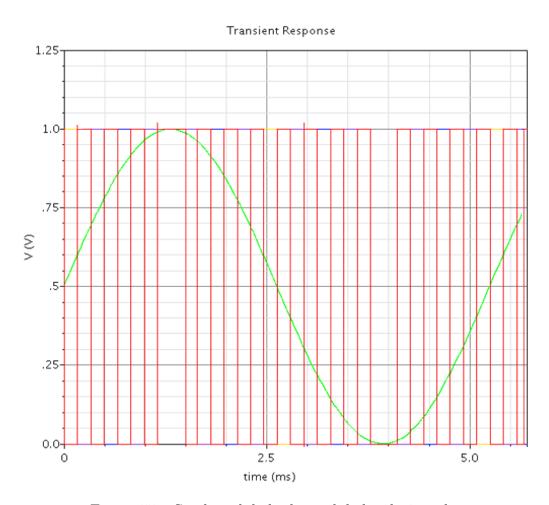

| Figura 55 – Sinal modulado do modulador de 1ª ordem                             | 34 |

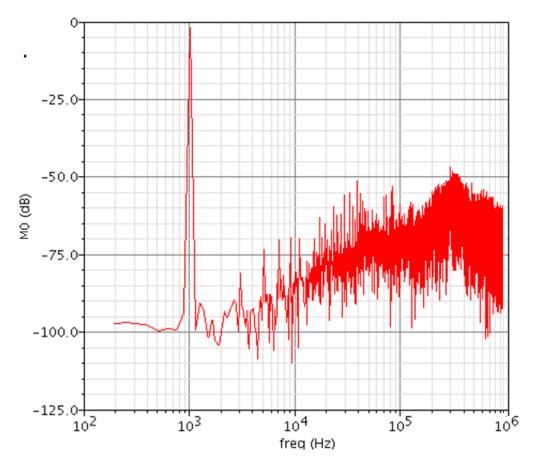

| Figura 56 – Transformada de Fourrier do sinal modulador de 1ª ordem 8           | 35 |

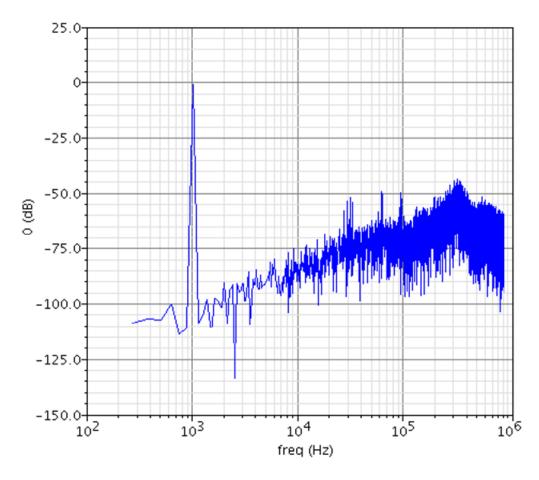

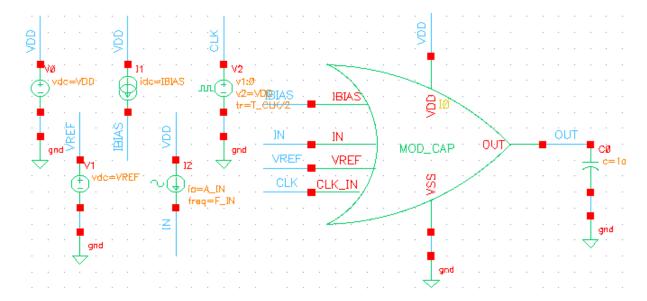

| Figura 57 — Esquemático do modulador de 1ª ordem Corrente-Tensão 8              | 36 |

| Figura 58 — Esquemático do modulador de 1ª ordem Corrente-Tensão 8              | 37 |

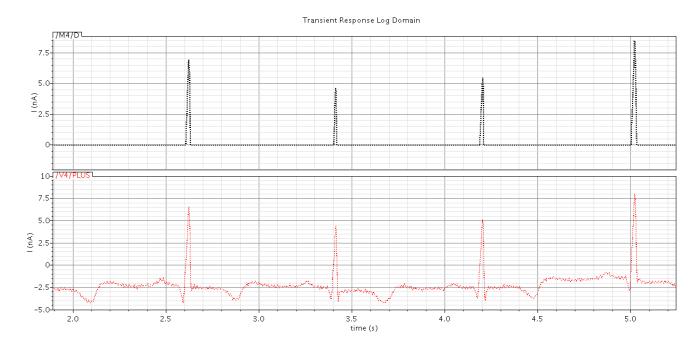

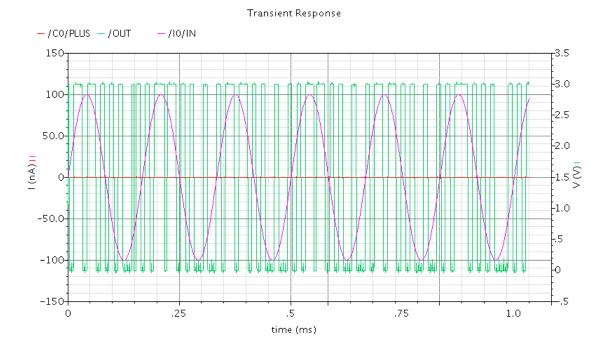

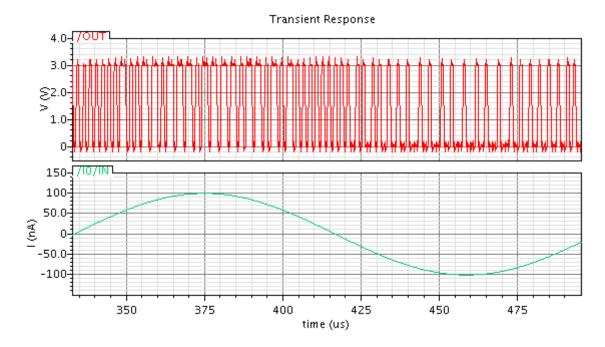

| Figura 59 — Resposta transiente ao modulador de 1ª ordem Corrente-Tensão 8      | 38 |

| Figura 60 — Resposta transiente ao modulador de 1ª ordem Corrente-Tensão: Sinal |    |

| modulado (Vermelho); Sinal de Entrada (Senoíde verde)                           | 38 |

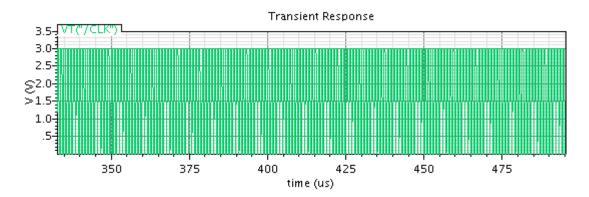

| Figura 61 – Resposta transiente ao modulador de 1ª ordem Corrente-Tensão: Clock |    |

| do Sistema à $F_{clock}$ 1MHz                                                   | 39 |

| Figura 62 – Transformada de $Fourrier$ do sinal modulado de 1ª ordem $$         | 90 |

| Figura 63 – Bloco do Conversor ADC completo de 1ª ordem (18)                    | 94 |

|                                                                                 |    |

|                                                                                 |    |

# Lista de tabelas

| Tabela 1 – | Comparação entre os diferentes métodos de conversão estudados (19) .               | 42 |

|------------|------------------------------------------------------------------------------------|----|

| Tabela 2 – | Cálculo da SNR para alguns bits                                                    | 46 |

| Tabela 3 – | Variações teóricas entre Corrente $(I_0)$ e frequência de corte $(F_c)$ utili-     |    |

|            | zando capacitor fixo de 50p                                                        | 75 |

| Tabela 4 – | Variações teóricas entre Capacitância (c) e frequência de corte ( $\mathbf{F}_c$ ) |    |

|            | utilizando corrente fixa de 10n                                                    | 75 |

| Tabela 5 – | Tabela de parâmetros da realização da DFT do modulador                             | 85 |

| Tabela 6 – | Descrição de Pinos e valores para o $testbench$ do modulador Corrente-             |    |

|            | Tensão                                                                             | 87 |

| Tabela 7 – | Tabela de parâmetros da realização da DFT do modulador                             | 89 |

# Lista de abreviaturas e siglas

ADC Conversor Analógico – Digital

AC Corrente Alternada

A/D Analógico - Digital

CI Circuito Integrado

CLK Clock do sistema

CMOS Complemetary Metal Oxide Silicon

DAC Conversor Digital - Analógico

DC Corrente Contínua

DECA Departamento de Estimulação Cardíaca Artificial

DNL Não Linearidade Diferencial

DR Dynamic Range

DTL Princípio Translinear Dinâmico

D/A Digital /Analógico

ECG Eletrocardiograma

ENOB Effective Number of Bits

Fb Frequência de Banda do Sinal

FFT Fast Fourier Transform

FIR Finite Impulse Response

Fm Frequência Máxima do Sinal

Fs Frequência de Amostragem

INL Não Linearidade Integral

L Length

LGR Lugar Geométrico das Raízes

LSB Least Significant Bit

MATLAB Matrix Laboratory

MOS Metal Oxide Semiconductor

MSB Most Significant Bit

NMOS Metal Oxide Semiconductor do tipo N

OVL Overloading Level

PMOS Metal Oxide Semiconductor do tipo P

SAR Succesive Aproximation Register

SNR Relação Sinal/Ruído

STL Princípio Translinear Estático

SUS Sistema de Saúde Unificado

S/H Sample and Hold

Vdd Tensão de Alimentação Positiva

W Width

# Lista de símbolos

| $\gamma$ | Letra grega minúscula ga  | ma   |

|----------|---------------------------|------|

| $\mu$    | Letra grega minúscula mi  | i    |

| $\Sigma$ | Letra grega maiúscula Sig | gma  |

| Δ        | Letra grega maiúscula De  | elta |

$\pi$

Letra grega minúscula pi

# Sumário

| 1       | INTRODUÇÃO                                                                |

|---------|---------------------------------------------------------------------------|

| 1.1     | Motivação e Justificativa                                                 |

| 1.2     | Objetivo Geral                                                            |

| 1.3     | Objetivos Específicos                                                     |

| 1.4     | Metodologia                                                               |

| 1.5     | Organização do Trabalho                                                   |

| I       | REVISÃO BIBLIOGRÁFICA E DETALHAMENTO DO PROJETO 33                        |

| 2       | REVISÃO BIBLIOGRÁFICA                                                     |

| 2.1     | Sinais                                                                    |

| 2.1.1   | Classificação dos Sinais                                                  |

| 2.1.1.1 | Sinal Contínuo ou Discreto no Tempo                                       |

| 2.1.1.2 | Sinal Analógico e Digital                                                 |

| 2.1.1.3 | Sinal Periódico e Aperiódico                                              |

| 2.2     | Tipos de Conversores Analógicos/Digitais (A/D)                            |

| 2.2.1   | Processo de Conversão A/D                                                 |

| 2.2.2   | Conversor A/D do Tipo <i>Two Step</i> (Rampa Dupla) ou Integrador         |

| 2.2.3   | Conversor A/D do Tipo <i>FLASH</i> ou Paralelo                            |

| 2.2.4   | Conversor A/D do Tipo Aproximação Sucessiva (SAR) 40                      |

| 2.2.5   | Conversor A/D do Tipo Sigma Delta ( $\Sigma\Delta$ ) 40                   |

| 2.2.6   | Quadro de Resumo das Comparações entre Conversores A/D 41                 |

| 2.3     | Parâmetros Fundamentais para Conversão de Sinais 43                       |

| 2.3.1   | Teorema da Amostragem                                                     |

| 2.3.2   | Ruído de Quantização                                                      |

| 2.3.3   | Não Linearidade Diferencial (DNL) e não Linearidade Integral/Acurácia Re- |

|         | lativa (INL)                                                              |

| 2.3.4   | Relação Sinal Ruído (SNR)                                                 |

| 2.3.5   | Número Efetivo de Bits (ENOB)                                             |

| 2.4     | Especificidade do Projeto                                                 |

| 2.4.1   | Anatomia Básica e Funcionamento do Coração                                |

| 2.4.2   | Aparelho de Marcapasso                                                    |

| 2.4.3   | Sinal de Eletrocardiograma (ECG)                                          |

| 3       | DETALHAMENTO DO PROJETO                                 | 51   |

|---------|---------------------------------------------------------|------|

| 3.1     | Exposição do Motivo                                     | . 51 |

| 3.2     | Arquitetura e Funcionamento do Conversor $\Sigma\Delta$ | . 51 |

| 3.2.1   | Estabilidade dos Moduladores                            | . 54 |

| 3.2.1.1 | Modulador de 1ª Ordem                                   | . 55 |

| 3.2.1.2 | Modulado de 2ª Ordem                                    | . 58 |

| 3.3     | ETAPA DIGITAL: FILTRO E DECIMAÇÃO DIGITAL               | . 61 |

| П       | PROJETO, IMPLEMENTAÇÃO E RESULTADOS                     | 63   |

| 4       | PROJETO DO CONVERSOR A/D $\Sigma\Delta$                 | 65   |

| 4.1     | Exposição do Motivo                                     | . 65 |

| 4.2     | Modulador $\Sigma\Delta$ em Modo Corrente               | . 65 |

| 4.3     | Corrente Sub-Limiar                                     | . 65 |

| 4.4     | Utilização do Domínio Logarítmico                       | . 66 |

| 4.5     | Circuitos Translineares                                 | . 66 |

| 4.5.1   | Princípio Translinear                                   | . 67 |

| 4.5.1.1 | Princípio Translinear Estático (STL)                    | . 67 |

| 4.5.1.2 | Princípio Translinear Dinâmico (DTL)                    | . 68 |

| 5       | IMPLEMENTAÇÃO EM TECNOLOGIA CMOS                        | 71   |

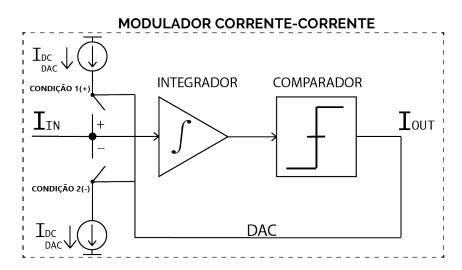

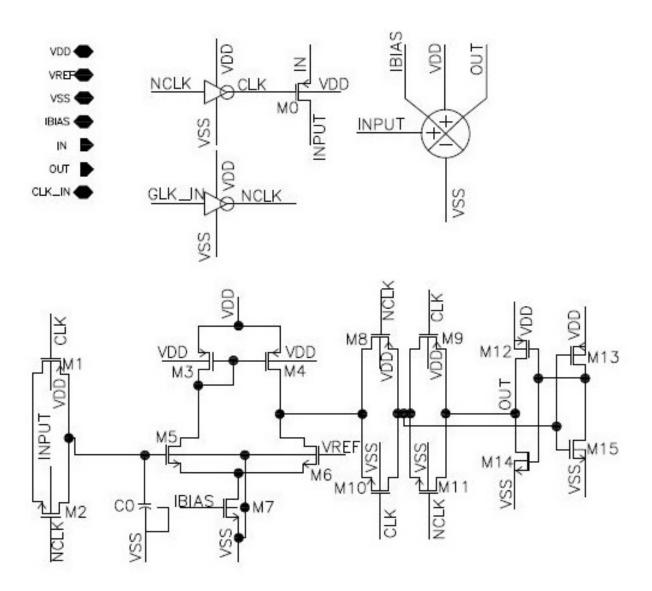

| 5.1     | O modulador Corrente-Corrente                           | . 71 |

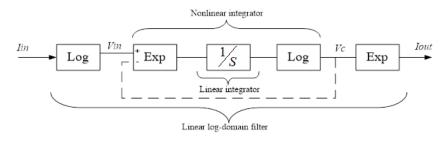

| 5.1.1   | Filtro e Integrador Translinear - Log-Domain            | . 72 |

| 5.1.2   | Comparador de Corrente                                  | . 78 |

| 5.1.3   | Diferenciador e Bloco de Memória (Latch)                | . 80 |

| 5.2     | O modulador Corrente - Tensão                           | . 80 |

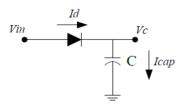

| 5.2.1   | Capacitor como Integrador                               | . 81 |

| 5.2.2   | DAC                                                     | . 82 |

| 5.3     | Resultados dos moduladores projetados                   | . 84 |

| 5.3.1   | Resultados: Modulador Corrente-Corrente                 | . 84 |

| 5.3.2   | Resultados: Modulador Tensão-Corrente                   | . 86 |

| Ш       | CONCLUSÃO E TRABALHOS FUTUROS                           | 91   |

| 6       | CONCLUSÃO E TRABALHOS FUTUROS                           | 93   |

| 6.1     | Conclusão                                               | . 93 |

| 6.2     | Trabalhos Futuros                                       | . 94 |

|         | REFERÊNCIAS                                             | . 97 |

# 1 INTRODUÇÃO

Este capítulo descreve a motivação e justificativa, objetivos gerais e específicos, metodologia e organização do trabalho de conclusão de curso de Engenharia Eletrônica da Universidade de Brasília. Neste trabalho é proposto a implementação de um projeto de um conversor analógico-digital do tipo Sigma-Delta de baixo consumo de potência para otimização de um aparelho marca-passo.

#### 1.1 Motivação e Justificativa

A engenharia eletrônica é capaz de projetar e desenvolver componentes e equipamentos microeletrônicos para diversas aplicações, e a engenharia biomédica é uma área que integra princípios das ciências exatas e ciências da saúde, desenvolvendo abordagens inovadoras aplicadas na prevenção, diagnóstico e terapia de doenças. Integrando as duas engenharias, o presente trabalho visa utilizar conhecimentos em microeletrônica para a aplicabilidade específica de um problema de insuficiência cardíaca, onde há um aumento da mortalidade devido a arritmias cardíacas caracterizadas por batimentos lentos ou por falha do mecanismo biológico.

Em 2015, segundo DECA(20), estimou-se que cerca de 22 milhões de pessoas eram portadoras de insuficiência cardíaca. O Brasil é o líder em número de mortes por insuficiência cardíaca no mundo, representando assim, uma em cada três internações no sistema de saúde unificado (SUS). Além disso, são cerca 100.000 novos casos por ano, sendo que 12,5% dos internados por causa da doença morrem nos hospitais brasileiros. (20)

Haja vista as consequências do problema, este trabalho propõe a otimização do aparelho de marca-passo por meio a microeletrônica analógica, visando a implementação de uma parte do projeto do sistema completo de um marca-passo. Esta parte se refere ao conversor analógico digital (A/D), responsável pela comunicação entre o mundo real e o mundo digital, em outras palavras, entre a recepção de um sinal analógico e todo o processo para devolver um sinal digital em forma de resposta. Existem inúmeros conversores A/Ds, mas de forma geral, pode-se definir os que trabalham à taxa de conversão igual a taxa de amostragem de Nyquist e aqueles que operam à taxa de sobreamostragem, também conhecida como Oversampling. O primeiro deles é rápido e geralmente utilizado para altas frequências, mas com limitação de resolução (10-12 bits), já o segundo, pode trabalhar com taxas muito maiores que a frequência de Nyquist, possui filtro digital em sua saída, o que ameniza a figura de ruído e filtra o ruído fora da banda, oferece alta resolução, baixo custo e

técnicas de Noise Shaping e Oversampling. SCHREIER, TEMES e NORSWORTHY(21).

Aparelhos de marca-passo são dispositivos, os quais, devem ser leves, pequenos, ter alta precisão e durabilidade, além de apresentar limites para consumo de energia e potência de acordo com a alimentação do aparelho, acarretando a necessidade de que tais dispositivos tenham baixa potência dissipada e eficiência energética. ROCHA(19).

Em síntese, para atender as especificidades do projeto para resolução do problema, aqui mencionados, o presente trabalho apresenta o modulador do conversor A/D do tipo Sigma Delta em modo corrente de baixo consumo de potência causando assim a otimização do circuito para maior durabilidade e precisão. Apresenta-se, também, outro circuito corrente-tensão para inovar o sistema do conversor.

#### 1.2 Objetivo Geral

O objetivo deste trabalho é o projeto dos moduladores de 1<sup>a</sup> e 2<sup>a</sup> ordem à nível de sistema de um conversor analógico-digital (ADC) de baixo consumo de potência específico para uso em um aparelho biomédico marca-passo. É necessário para se atingir o objetivo, o entendimento da topologia do conversor Sigma-Delta, e também, testes em simulações e o desenvolvimento do circuito modulador de 1<sup>a</sup> ordem utilizando a ferramenta CADENDE TSMC  $0.13\mu$ m em modo corrente e em modo corrente-tensão com a tecnologia CMOS (Complemetary Metal Oxide Silicon).

#### 1.3 Objetivos Específicos

Os objetivos específicos são baseados em resultados do objetivo geral e podem ser definidos como as etapas do projeto deste trabalho:

- Escolha da aplicação do projeto;

- Entendimento do processo de conversão ADC;

- Pesquisa referente a tipos de conversores e escolha do mais adequado ao projeto;

- Detalhamento da topologia escolhida;

- Simulação para validação da escolha da topologia utilizando diagrama de blocos na ferramenta Simulink do software MATLAB;

- Obtenção de parâmetros de projeto suficientes para prosseguir na construção do circuito;

- Simulação e projeto dos moduladores de 1<sup>a</sup> ordem do circuito em modo correntecorrente e corrente-tensão utilizando o software CADENCE e tecnologia CMOS;

1.4. Metodologia 29

• Exposição dos resultados do funcionamento dos moduladores em nível transístor;

• Implementação em projeto futuro: decimador digital, layout do circuito integrado (CI) e envio para construção do CI em fábrica para validação e testes em trabalho de mestrado.

#### 1.4 Metodologia

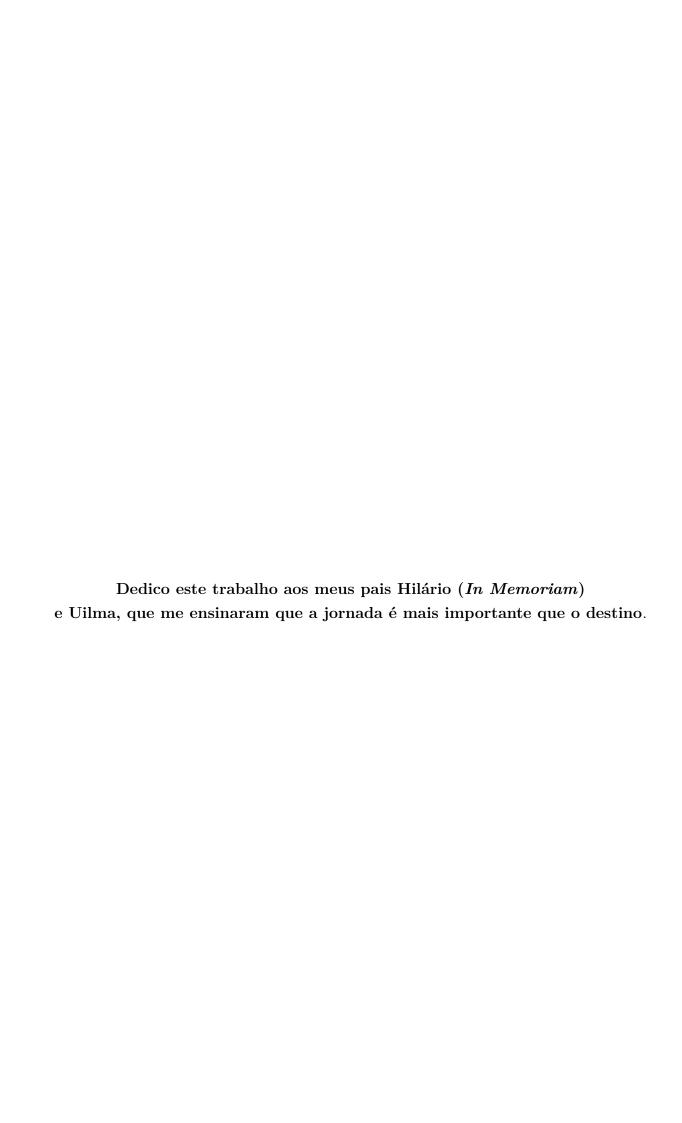

Para a organização do trabalho, aplicou-se a abordagem *Top-Down* na qual se utiliza estratégias de processamento de informação e ordenação de conhecimento a partir da fragmentação de um sistema até a compreensão de todos os seus subsistemas. De outra maneira, isto é, um passo a passo, para apresentação do produto, no caso o circuito integrado do conversor Sigma Delta, detalhando seus parâmetros de níveis básicos até realizações de simulações e projeto para a construção, desenvolvimento e verificação do mesmo.

Segundo Karplus (22), um modelo é definido como a descrição das relações entre objetos que compõem um sistema; este sistema é o conversor Sigma-Delta. Este trabalho consiste em apresentar duas das três etapas de modelagem: modelagem verbal, modelagem diagramática e modelagem física. Dentre as três, aborda-se aqui, a modelagem verbal por meio de referências bibliográficas para a descrição do sistema em estudo e a modelagem diagramática que consiste na formação de blocos para explicação do sistema. O diagrama Top-Down do trabalho pode ser observado na Figura 1.

A partir da Figura 1 e usufruindo da abordagem Top-Down e do modelo de Kar-plus, definiu a seguinte metodologia de trabalho em 12 etapas:

- 1. Interesse em resolver um problema que afeta 22 milhões de pessoas;

- 2. Levantamento bibliográfico do funcionamento do conversor analógico-digital;

- 3. Descrição de topologias e análises de parâmetros;

- 4. Escolha da topologia mais adequada para a resolução do problema;

- 5. Simulação em alto nível utilizando o software MATLAB;

- Otimização e testes da simulação em alto nível com diagrama de blocos;

- 7. Comprovação em alto nível da estabilidade do conversor escolhido;

- 8. Substituição da simulação em alto nível para nível de transistores;

- 9. Simulação a nível de transistores utilizando a ferramenta CADENCE;

- 10. Validação a partir de uma nova verificação a nível de transistores;

Figura 1 – Metodologia Top/Down para a implementação do conversor ADC Sigma – Delta. (1)

- 11. Documentação do fluxo de projeto;

- 12. Planejamento para implementação de Layout e testes em trabalhos futuros.

Sendo definidas as etapas em tópicos, tem-se a modelagem verbal equivalente aos tópicos 1 a 4 e também 11, modelagem diagramática dos tópicos 5 a 10 e modelagem física referente ao tópico 12, o qual é uma proposta para trabalhos futuros.

#### 1.5 Organização do Trabalho

O trabalho está organizado em três partes distintas. Onde a primeira parte é referente ao capítulo 1 ao 3, a segunda parte os capítulos 4 e 5 e terceira o capítulo 6.

Neste primeiro capítulo apresenta-se a introdução, motivação e justificativa, objetivos gerais e específicos, metodologia e organização do trabalho.

O segundo capítulo apresenta uma revisão bibliográfica expondo desde o que são sinais até seu tratamento de conversão analógico-digital e seus parâmetros, além de demonstrar topologias diferentes de conversores para a escolha da melhor aplicabilidade ao estudo, demonstrado também aqui, do marca-passo.

O terceiro capítulo relata a justificativa da escolha do conversor Sigma-Delta, cálculos de parâmetros importantes de projeto, descrição da parte analógica e parte digital

do conversor escolhido e validação das justificativas utilizando simulações no software MATLAB  $\circledR$ .

O quarto capítulo é delimitado à descrição de princípios fundamentais para a implementação, no quinto capítulo, dos blocos individuais dos moduladores de 1ª ordem em modo corrente- corrente e corrente-tensão.

O quinto capítulo apresenta a descrição individual dos blocos da implementação do modulador operando a ferramenta CADENCE Virtuoso com tecnologia CMOS TSMC  $0.13\mu m$ . Os circuitos são implementados e testados para validação em nível transístor.

O sexto, e último, capítulo consiste na apresentação das conclusões sobre o trabalho realizado, as propostas futuras de implementação e o mapa de planejamento da finalização do projeto.

# Parte I REVISÃO BIBLIOGRÁFICA E DETALHAMENTO DO PROJETO

## 2 REVISÃO BIBLIOGRÁFICA

Este capítulo é delimitado à revisão bibliográfica referente a conversores analógico-digitais, com ênfase ao conversor analógico-digital do tipo Sigma-Delta com baixo consumo de potência. Demonstra-se aqui, alguns parâmetros para o projeto de um conversor analógico-digital e também, revisões a respeito dos sinais analógicos e digitais com destaque ao sinal do eletrocardiograma e conceitos fundamentais sobre o coração e o seu funcionamento.

#### 2.1 Sinais

O termo sinal é a representação qualitativa ou quantitativa a qual porta uma informação, ou também, de como um parâmetro varia em relação ao outro. Essa representação possui classificações e deriva de diferentes origens, seja mecânica ou biológica, para que se possa entender, modelar, representar ou transmitir uma informação. Esta informação é interpretada por meios elétricos e podem ou não variar de acordo com o tempo e com a distância.

#### 2.1.1 Classificação dos Sinais

Existem diversas classificações de sinais, contudo, para o escopo deste trabalho de conclusão de curso, limita-se à classificação, de maneira geral, como sinal contínuo ou discreto no tempo, sinal analógico, digital, periódico e aperiódico.

#### 2.1.1.1 Sinal Contínuo ou Discreto no Tempo

O sinal o qual sempre é especificado o seu valor no tempo t é o sinal em tempo contínuo. O sinal o qual é especificado somente o seu valor discreto em t é o sinal em tempo discreto. (2) Ou seja, um sinal discreto é uma função proveniente de outra função, real, a qual exibe uma sequência de Deltas de Dirac coincidentes com o valor da função, demonstrando assim, valores em pontos isolados. Já o sinal contínuo é aquele no qual se apresenta uma função inteira e se pode acompanhá-la em sua forma real e direta. Classificam-se esses, ao longo do tempo.

#### 2.1.1.2 Sinal Analógico e Digital

Classificam-se estes por suas amplitudes, ou seja, o sinal cuja amplitude pode ter diversos valores, até mesmo infinitos, em uma faixa contínua é o sinal analógico. O sinal digital, por sua vez, é aquele no qual existem finitos valores de amplitude. (2)

#### 2.1.1.3 Sinal Periódico e Aperiódico

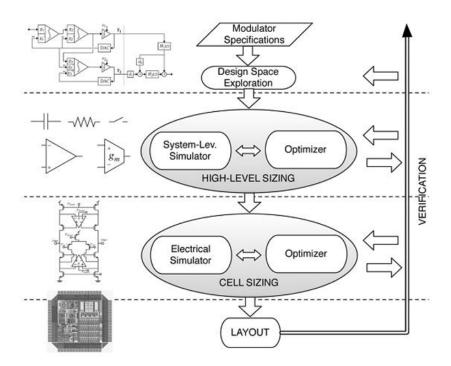

O sinal periódico é determinado pela repetição ou período, no qual demonstra a mesma característica, ou seja, se ele se repete ao longo do tempo. E o sinal aperiódico é aquele no qual não se tem uma forma específica, ou tempo para repetição. A Figura 2 abaixo demonstra os tipos de sinais apresentados.

Figura 2 – Exemplos de sinais (a) Analógico e contínuo no tempo, (b) Digital e contínuo no tempo, (c) Analógico e discreto no tempo. (d) Digital e discreto no tempo. (2)

#### 2.2 Tipos de Conversores Analógicos/Digitais (A/D)

Existem diversos tipos de conversores analógicos-digitais para diferentes aplicações e que se adequam de maneira apropriada a especificações de projetos. Para a escolha do conversor ideal para aplicação e tratamento no sinal de ECG para um marca-passo analisou-se os demais tipos, verificando, principalmente, resolução, velocidade e baixo consumo de potência.

#### 2.2.1 Processo de Conversão A/D

Utilizar sinais analógicos é o mesmo que trabalhar com diversas e até infinitas amplitudes em uma faixa contínua, já o uso do sinal digital é aquele no qual os valores das amplitudes são finitos e discretos. Ou seja, de maneira geral, manusear um sinal digital é mais prático quando comparado a um sinal analógico. O processo de conversão analógico-digital (A/D) é realizado para que o trabalho com sinais seja assim facilitado.

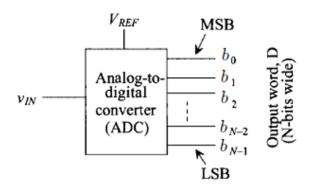

A conversão por sua vez é dada de maneira sistêmica por meio de um conversor A/D, esse é responsável por receber um sinal analógico e devolver um sinal digital. De maneira geral, BAKER(3) define que um conversor tem uma estrutura básica de acordo com a Figura 3.

Figura 3 – Representação geral de um bloco de conversão A/D.(3)

A Figura 3 é um bloco de conversão A/D onde se introduz uma entrada ( $V_{IN}$ ) e também se mantém uma tensão de referência  $V_{REF}$ , define-se  $b_0$  como o MSB e o  $b_{N-1}$  como o LSB e D como uma palavra de N bits. Analisando de forma mais detalhada, embora genérica, a parte interna do conversor A/D tem-se a estrutura da Figura 4.

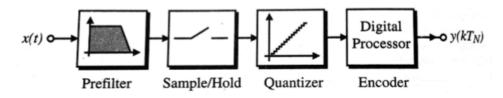

Figura 4 – Descrição de forma sucinta e genérica de um conversor A/D. (4)

Este processo evidenciado na Fig. 4 é formado por blocos; o primeiro bloco tem a função de amenizar ou evitar o Aliasing, o segundo, o bloco integrado Sample/Hold (S/H) é responsável pela amostragem do sinal analógico e também por mantê-lo constante no valor amostrado. Por fim, o terceiro bloco Quantizer é o que realiza a quantização do sinal. A última etapa (quantização) realiza divisões do sinal em intervalos, e quando obtém amostras do sinal as aloca no valor mais próximo do mesmo. O nível de quantização é atribuído em uma codificação binária de N bits, as distâncias entre os níveis não são necessariamente idênticas, ou seja, têm-se 2N intervalos uniformes, sendo que N é o número de bits do código digital de saída. Para que o processo de conversão aconteça é necessário que haja um conversor do tipo A/D, este são detalhados e evidenciados nas seções 2.2.2 a 2.2.5.

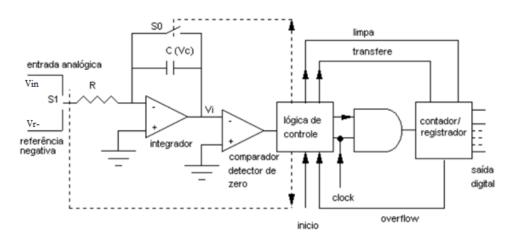

#### 2.2.2 Conversor A/D do Tipo Two Step (Rampa Dupla) ou Integrador

O conversor do tipo  $Two\ Step$ , de acordo com a Figura 5, funciona a partir de duas integrações. Por análise, nota-se que S0 é acionada para que haja descarga do capacitor e  $S_1$  se encontra na entrada analógica  $(V_{IN})$  a qual se conecta a entrada inversa do integrador por um tempo até que o contador esteja preenchido.

O intervalo entre o preenchimento do contador faz com que capacitor seja carregado e que o integrador gere uma rampa decrescente na sua saída. Quando o último preenchimento do contador acontece (determinado pelo final do tempo designado), esse é zerado e gerará um pulso de *overflow*. Então, quando o sinal de *overflow* é recebido, a contagem estaciona e a chave  $S_1$  é alternada para a tensão de referência negativa  $(V_{r-})$ .

Quando esta tensão negativa é inserida, o integrador descarrega o capacitor e entrega uma rampa crescente em sua saída, durante um novo intervalo de tempo. Durante esse novo intervalo de tempo, os pulsos de *clock* são contados até que se realize um total proporcional à Vin. Quando o tempo termina, a tensão da rampa é zero, e o comparador detector de zero ativa a lógica de controle que finaliza a conversão e o processo pode ser refeito com uma nova Vin. (9)

Figura 5 – Modelo básico de Conversor Two Step. (5)

Este conversor é taxado como lento, devido à necessidade de dois tempos para que a conversão seja completada, e de alta resolução (1ms para 20 bits), e é também insensível à tolerância de R e de C e frequência do *clock* (tornando-o independente da mesma), e possui baixo *offset* e erro de ganho, e por ser do tipo rampa, apresenta uma linearidade alta. (9)

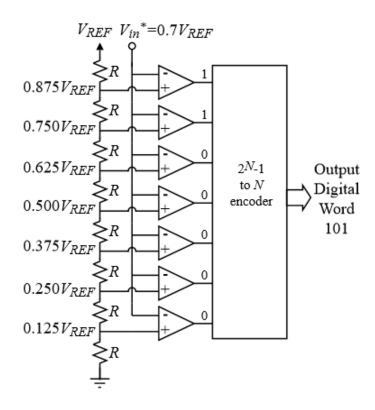

#### 2.2.3 Conversor A/D do Tipo FLASH ou Paralelo

O conversor do tipo Flash, de acordo com a Figura 6, funciona a partir do uso de  $2^N$ -1 comparadores para um conversor de N bits.

Figura 6 – Topologia de conversor A/D tipo FLASH. (6)

Por análise da Figura 6, entende-se que o conversor funciona em primeira instância do relógio, e que a entrada analógica é amostrada e injetada aos comparadores. Assim, é obtido um código diferente da numeração binária, tornando necessário utilizar a rede de codificação digital (encoder), que por sua vez converte a palavra binária de saída. É importante destacar que o código binário deve ficar disponível em suas entradas enquanto a conversão acontece porém não deve haver perda de informação no processo, e, isso é feito a partir da inserção de latch's que aprisionam a palavra que será convertida. (23)

Esse é considerado o conversor mais rápido devido a sua topologia, contudo o mesmo necessita de uma grande quantidade de comparadores e tem resolução aproximada de 8 bits. Essa grande quantidade de comparadores deriva-se da necessidade de utilizar  $2^N$  -1 comparadores para um conversor de N bits, ou seja, para um conversor de 3 bits são necessários 7 comparadores e para um conversor de 8 bits são necessários 257. (9) Assim, o mesmo demanda uma utilização de área maior e consumo alto, o que não o limita, mas não o favorece em relação ao demais.

#### 2.2.4 Conversor A/D do Tipo Aproximação Sucessiva (SAR)

O conversor do tipo SAR, de acordo com a Figura 7, funciona a partir de uma conversão rápida que pode chegar a 100 mil ou mais conversões por segundo. Para essa topologia, um sistema de N bits necessita de um tempo de conversão de N períodos de clock. (24)

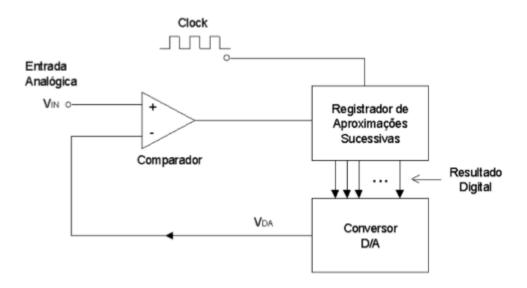

Figura 7 – Topologia de conversor por aproximação sucessiva SAR. (7)

O conversor SAR é semelhante a um registrador de deslocamento, e este compara N vezes a entrada  $V_{IN}$  à tensão de referência  $V_{REF}$  a partir do acionamento do tempo de clock, colocando-o em 0. A primeira etapa é a comparação que verifica se  $V_{IN}$  é maior ou menor que  $\frac{1}{2}$  de  $V_{MAX}$  (tensão máxima de entrada do conversor). A segunda etapa analisa em qual  $\frac{1}{4}$  da variação  $V_{IN}$  se enquadra, vale ressaltar que em cada etapa que ocorre de modo sucessivo, acontece um estreitamento de  $\frac{1}{2}$  na faixa dos possíveis resultados. A lógica de controle assume o MSB como 1 e os outros como 0, se a saída do comparador for alta, a lógica de controle determina que MSB será 1 e se for baixa, MSB será 0. Esse processo acontece de modo sucessivo, até que todos os N bits sejam aproximados. (23)

#### 2.2.5 Conversor A/D do Tipo Sigma Delta $(\Sigma\Delta)$

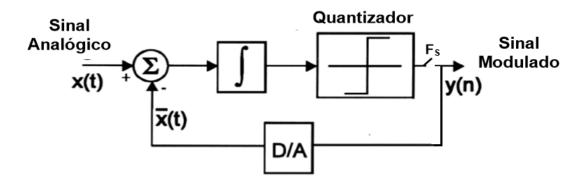

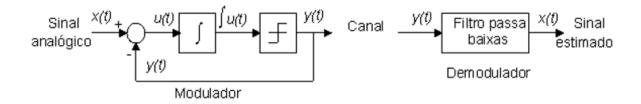

O conversor do tipo  $\Sigma\Delta$ , de acordo com a Fig. 8, funciona a partir de taxas de amostragem com frequências superiores às frequências de Nyquist, também conhecido como sobreamostrados, utiliza-se também uma realimentação negativa e filtragem digital.

De maneira geral e sucinta, o conversor Sigma Delta possui duas partes: uma analógica e outra digital. A parte analógica é constituída de um modulador do tipo  $\Sigma\Delta$  e responsável por receber o sinal inserido no sistema e dirigi-lo ao modulador e posteriormente ao integrador. Neste processo o sinal é amostrado e quantizado e caso necessário o

Figura 8 – Modulação do tipo Sigma-Delta (4)

processo é repetido. Já na parte digital, constitui-se de um filtro passa-baixa o que devolve o sinal à taxa de amostragem de *Nyquist* sem perda de informação. (25)

Esses conversores são capazes de realizar conversões de até 24 bits. Funcionam a partir de um modulador Sigma-Delta, um filtro digital, o qual retira o ruído fora da largura de banda e um decimador que funciona como um filtro passa-baixas. Apresenta alta resolução, velocidade razoável pois varia de acordo com a quantidade de bits, baixo custo e alta integração. Além de portar técnicas de oversampling e noise shaping, as quais são características responsáveis por fazer com que a densidade de ruído de quantização se propague por uma larga banda de frequência e também, por modificar a densidade de ruído de maneira com que este aumente em altas frequências e diminua em baixas frequências, respectivamente. (9)

Os conversores desta topologia usufruem de apenas 1 bit, a sua SNR seria igual a 7,78 dB o que é bastante baixo. Contudo, devido às características de *Oversampling* o ruído é colocado em altas frequências do espectro e não somente espalhado por todo o espectro e esse efeito é conhecido como *noise shaping*. Com esse ruído aglomerado em uma faixa de frequência acima do dado amostrado, tem-se a facilidade de construir um filtro para a remoção do mesmo, aumentando assim a relação entre sinal e ruído (SNR). Esse tipo de filtro, como dito anteriormente, é um filtro passa baixas e compreende a etapa digital do conversor  $\Sigma\Delta$ .

Dentre as topologias apresentadas de forma sucinta até aqui, este último foi o conversor escolhido para a aplicação de baixo consumo de potência no aparelho de marcapasso. E será detalhado no capítulo 3.

#### 2.2.6 Quadro de Resumo das Comparações entre Conversores A/D

Visto que existem conversores sobreamostrados e aqueles que trabalham na frequência de *Nyquist* e analisando os requisitos do projeto, optou-se pela escolha do modulador do tipo Sigma-Delta, uma vez que esse apresenta alta resolução, baixo consumo de potên-

cia e velocidade razoável. A Fig. 9, adaptada de BEZERRA(8) evidencia as comparações entre velocidade potência e resolução.

Figura 9 – Comparação entre parâmetros de um conversor ADC (8)

A Figura 9 evidencia que o Sigma-Delta apresenta alta resolução, baixo consumo de potência e uma velocidade razoável em relação aos demais conversores aqui comparados.

Para que a escolha fosse realizada com sucesso e segurança, verificaram-se todos os parâmetros necessários para validação da escolha, com auxílio de estudos aqui realizados. Na tabela 1, SILVA(13) evidencia, com base em BEZERRA(8), uma forma comparativa entre os principais tipos de conversores.

| Tabela 1 – 0 | Comparacao | entre os   | diferentes  | metodos | de | conversao   | estudados | 119  | 1 |

|--------------|------------|------------|-------------|---------|----|-------------|-----------|------|---|

| Tabota I     | Comparação | CITUI C OD | CITCL CITCO | modado  | uc | COLLACIDAGO | Coudados  | 1 10 | , |

|                                                 | Aproximações<br>Sucessivas - SAR                        | Paralelo - Flash                                                                                   | Rampa Dupla                                                    | Sigma-Delta $\Sigma\Delta$                                                                                 |

|-------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Facilidade de<br>Interface com o<br>Processador | Média                                                   | Alta                                                                                               | Média                                                          | Alta                                                                                                       |

| Tempo de Conversão $(\frac{1}{fs})$             | Aumenta<br>linearmente com o<br>aumento da<br>resolução | Tempo de<br>conversão não<br>muda com a<br>maior resolução                                         | Tempo de conversão dobra a cada aumento de um bit na resolução | Baixo, para resolução < 14 bits  Médio, para 14 bits < resolução < 16 bits  Alto, para 16 bits > resolução |

| Resolução                                       | Médias a altas<br>8 a 16 bits                           | Tipicamente<br>limitado a<br>resolução de 8 bits                                                   | Altas                                                          | Altas                                                                                                      |

| Tamanho                                         | Aumenta<br>linearmente com o<br>aumento da<br>resolução | (2 <sup>N</sup> - 1) de<br>comparadores,<br>tamanho aumenta<br>exponencialmente<br>com a resolução | Tamanho não altera substancialmente com o aumento da resolução | Tamanho não altera substancialmente com o aumento da resolução                                             |

| Custo                                           | Elevado                                                 | Alto                                                                                               | Baixo                                                          | Médio                                                                                                      |

Assim, o conversor do tipo Sigma-Delta foi escolhido para aplicação de um projeto de marca-passo de baixo consumo de potência. O conversor será detalhado no capítulo 3.

#### 2.3 Parâmetros Fundamentais para Conversão de Sinais

É importante ressaltar que para se converter um sinal analógico em digital é preciso ter o conhecimento de alguns parâmetros e métodos para que o processo seja efetuado. Os quais são demonstrados, de forma resumida, nesta seção 2.3.

#### 2.3.1 Teorema da Amostragem

O teorema da amostragem de *Nyquist-Shannon*, o qual é popularmente conhecido como Teorema de *Nyquist* é de suma importância quando se trata de processamento de sinais. Amostrar um sinal significa converter um sinal em uma sequência numérica, ou seja, processar um sinal contínuo no tempo em um sinal discretizado.

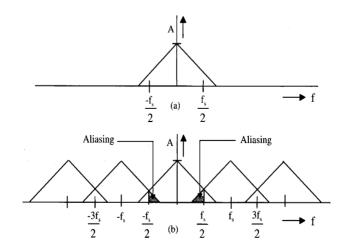

O teorema demonstra que um sinal analógico limitado em banda e que foi amostrado pode ser perfeitamente recuperável a partir de uma sequência infinita de amostras, isto condicionado a uma taxa de amostragem maior que 2 vezes a Fm (Frequência Máxima do sinal original) amostradas por segundo. Isto é, um sinal só pode ser reconstruído perfeitamente se, e somente se, a sua taxa de amostragem for maior ou igual a 2 vezes a Fm. Contudo, existe um problema quando não se satisfazem as condições necessárias para o funcionamento do teorema, esse é conhecido como aliasing demonstrado na Fig. 10.

Figura 10 – (a) Exemplo da entrada de um sinal (b) Espectro do sinal amostrado. (9)

Este fenômeno conhecido como aliasing é visível, pois se notam cópias adjacentes e sobrepostas à função original. Para resolução desse problema utiliza-se um filtro antialiasing, que, por sua vez, limita a largura de banda do sinal fazendo com que este satisfaça os critérios da amostragem adequada ao mesmo. Quando se pretende reduzir o ruído de quantização deve-se aumentar a taxa de amostragem, o que é denominado OverSampling.

#### 2.3.2 Ruído de Quantização

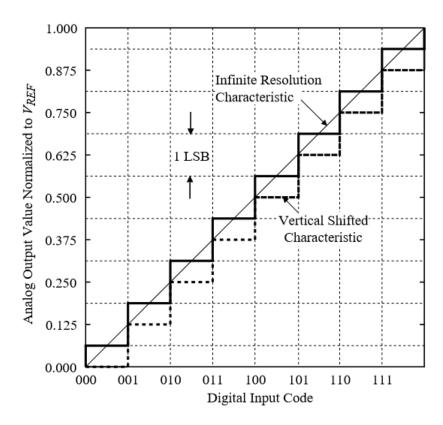

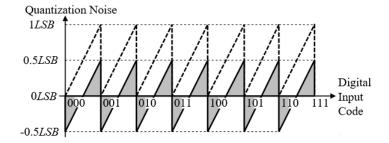

O ruído de quantização é uma incerteza de digitalização de um valor analógico com uma finita resolução de conversão assim demonstradas na Fig. 11. (6)

Figura 11 – Características ideais de entrada e saída de uma DAC de 3-bits. (6)

A Figura 11 evidencia que o erro ou ruído de quantização é a diferença entre o sinal de entrada (linha contínua e em formato rampa) e representação analógica do sinal de saída em forma digital. É importante ressaltar que o MSB (The Most Significant Bit), é o bit mais significante e tem grande influência na saída analógica, e que o LSB (The Least Significant Bit) é o bit que possui menor influência na saída analógica. A Figura 12 é a demonstração de uma forma de onda de dente de serra de pico-a-pico com valor de 1 LSB, onde sua acurácia absoluta é de  $\pm 0.5$  LSB. (6)

Figura 12 – Dente de serra com valor de 1LSB pico a pico em uma DAC de 3-bits. (6)

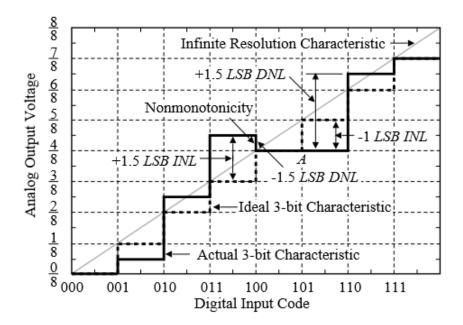

# 2.3.3 Não Linearidade Diferencial (DNL) e não Linearidade Integral/Acurácia Relativa (INL)

O INL é a máxima diferença entre a atual e a ideal resolução característica medida verticalmente, e o DNL como a medida de separação entre os níveis adjacentes medidos em cada degrau vertical. A Figura 13 evidencia de forma clara como se deve analisar o INL e o DNL, no caso em uma DAC de 3 bits. (6)

Figura 13 – INL, DNL, Monotonicidade em um DAC de 3 bit. (6)

A Figura 13 apresenta  $2^N$ , onde N é o número de bits, divisões de saída analógica de oito divisões na entrada digital. Ou seja, para um DAC de 3 bits, são  $2^3=8$  divisões e apresenta-se  $\pm$  1,5 LSB DNL e  $\pm$  1 LSB INL. O DNL pode ser calculado a partir da seguinte Eq. 2.1:

$$DNL = V_{CX} - V_S = \left(\frac{V_{CX} - V_S}{V_S}\right) V_S = \left(\frac{V_{CX}}{V_S} - 1\right) LSBs$$

(2.1)

Podendo assim, DNL ser negativo ou positivo, de acordo com a mudança de entrada em relação à saída. Se essa variação for menor que 1LSB, o DNL será negativo, caso contrário, positivo. A análise do INL e DNL é fundamental para que se conheça a tolerância e precisão do componente projetado. (6)

#### 2.3.4 Relação Sinal Ruído (SNR)

A relação sinal ruído (SNR) é dependente do tempo de estabilização, da linearidade e da resolução do ADC. (6) Este é calculado a partir da Eq. 2.2:

$$SNR = n \cdot 6.02 + 1.72dB \tag{2.2}$$

A partir da equação, pode-se notar que a SNR cresce 6.02 vezes o tamanho de N e adiciona uma parcela de 1.76, tudo isso em decibéis. Com o aumento da razão entre o SNR e um fator igual a  $10\log_{10}(k)$  é denominado efeito de sobre-amostragem. Levando isso em consideração, demonstra-se aqui:

| N (bits) | dB    |

|----------|-------|

| 4        | 25,84 |

| 5        | 31,86 |

| 6        | 37,88 |

| 7        | 43,90 |

| 8        | 49,92 |

| 9        | 55,94 |

Tabela 2 – Cálculo da SNR para alguns bits.

#### 2.3.5 Número Efetivo de Bits (ENOB)

Outro parâmetro fundamental para realizar comparações entre resolução e estabilização de um conversor A/D é o número efetivo de bits (ENOB), esse é calculado pela Eq. 2.3:

$$ENOB = \frac{SNDR_{medido} - 1.76}{6.02} \tag{2.3}$$

onde SNDR é o SNR calculado na secção 2.2.4 Avalia-se a resolução e a estabilização com base no ENOB, pois ele define quantos bits são realmente usados no circuito, o que também define qual a margem de erro e de bits inutilizados.

Existem outros diversos parâmetros para o projeto de um conversor analógico digital, contudo para este trabalho de conclusão de curso não é necessária a explicação detalhada dos mesmos.

#### 2.4 Especificidade do Projeto

Sabe-se até aqui, que o processo de conversão analógico-digital é de suma importância para o mundo atual e que a microeletrônica é fundamental para que esse processo aconteça de forma eficaz. Tendo em vista todos os parâmetros necessários e o conversor escolhido é notório explorar a especificidade do projeto. Ou seja, aqui se demonstram a estrutura e o funcionamento básico do coração e do marca-passo, ressaltando também como o sinal do eletrocardiograma influencia no projeto.

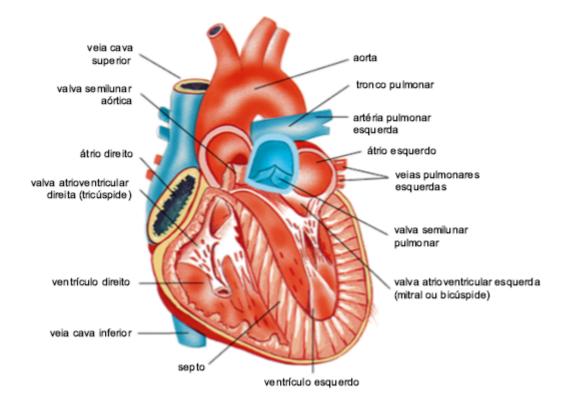

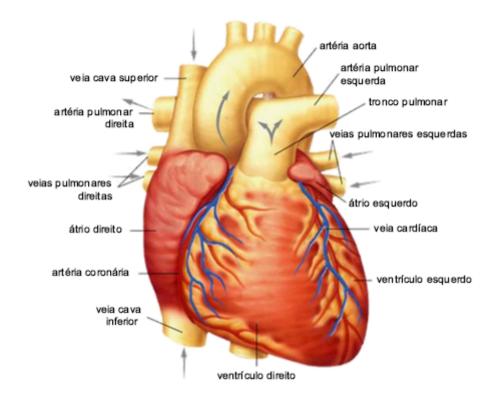

#### 2.4.1 Anatomia Básica e Funcionamento do Coração

O coração humano, com tamanho comparável a um punho fechado, tem cerca de 400g e localiza-se na parte central no peito, sob o osso esterno, com a exterminada inferior deslocada minimamente para a esquerda. Esse é uma potente bomba propulsora de sangue e é formado por tecido muscular estriado cardíaco, miocárdio e quatro cavidades internas. Estas cavidades são chamadas de câmaras internas que se dispõem entre superiores e inferiores, direitas e esquerdas. Existem diferenças entres as disposições e estas são derivadas das suas funções específicas. (26)

As câmaras inferiores são denominadas ventrículos cardíacos e apresentam paredes espessas, em contrapartida, as câmaras superiores, denominadas átrios cardíacos, apresentam paredes mais finas que as câmaras inferiores. Os átrios, por sua vez, são responsáveis por bombear sangue para os ventrículos, e o ventrículo esquerdo bombeia sangue para todo o corpo e, o direito, para os pulmões. (10)

As comunicações entre átrios e ventrículos ocorrem de maneira organizada, ou seja, o átrio esquerdo se comunica com o ventrículo esquerdo e o átrio direto se comunica com o ventrículo direito. Essas comunicações, através de válvulas, fazem com que o sangue circule de maneira sistêmica e em um único sentido, essas válvulas são denominadas válvula mitral (comunicação esquerda) e válvula tricúspide (comunicação direita). Essas e as demais especificações já feitas, são demonstradas nas Figuras 14 e 15.

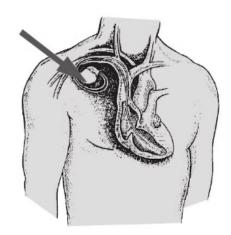

Figura 14 – Coração humano: aspecto interno. (10)

Figura 15 – Coração humano: aspecto externo. (10)

Os movimentos do sangue no organismo humano são sustentados pelas contrações da musculatura do coração. As contrações acontecem de maneira rítmica em um processo de diástole e sístole, podendo essas serem atriais ou ventriculares.

A sístole acontece quando a musculatura contrai e o sangue é expulso do coração e a diástole, quando a musculatura relaxa e o sangue invade as câmaras cardíacas. A sequência de diástoles e sístoles forma o ciclo cardíaco.

Quando uma pessoa está em repouso, relaxada, ou estressada, ou faz determinada atividade física, a frequência cardíaca pode variar, ou seja, é afetada diretamente pelo seu estado emocional e físico. A frequência cardíaca é o número de vezes em que acontece a contração do coração por unidade de tempo; ela é controlada por um conjunto de células musculares, localizado próximo à junção entre o átrio direito e a veia cava superior, a qual é denominada nó sinoatrial ou marca-passo. O marca-passo é responsável por enviar um estimulo elétrico que viaja diretamente para a musculatura do átrio e provoca a sua contração, e o nó atrioventricular é responsável por receber esse estímulo e ajudar a musculatura dos ventrículos a entrar em sístole, fazendo assim, com que o coração funcione.

#### 2.4.2 Aparelho de Marcapasso

O aparelho de marca-passo é um dispositivo eletrônico do ramo biomédico com a função primordial de regular o ritmo cardíaco. Esse substitui o marca-passo natural quando este não é capaz de enviar o estimulo necessário para que haja contração da musculatura do coração.

Esse dispositivo é indicado em casos de nó sinusal, hipersensibilidade ao seio carotídeo, bloqueio atrioventricular, entre outros que fazem o paciente perder a capacidade de realizar um número de batimentos cardíacos considerável normal. O normal de batimentos cardíacos é de 70 a 80 batimentos por minuto em rotinas diárias, de 35 a 50 durante o sono e 180 batimentos durante uma atividade física. Quando esse ritmo está abaixo do normal, e apresenta uma lentidão periódica ou constante (bradicardia), causando cansaço, palpitações, tonturas ou desmaios, o uso de marca-passo é fundamental. (26) O aspecto de um aparelho deste modelo pode-se visualizar na Figura 16.

Figura 16 – Visualização de um marca-passo e implantação do dispositivo no corpo humano. (11)

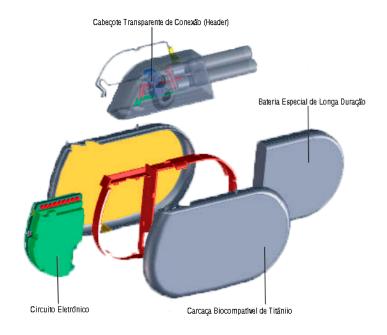

Esses dispositivos são construídos, geralmente, de titânio reduzindo assim o risco de rejeição do corpo humano, duram entre 5 e 15 anos, dependendo da necessidade de ativação do aparelho pelo coração. Eles são formados por um dispositivo eletrônico e um ou dois cabos de eletrodos. O dispositivo contém a circuitaria eletrônica e uma bateria, demonstrando uma lógica digital e analógica demonstrados na Figura 17. O cabo de eletrodo é responsável por transportar estimulo elétrico do marca-passo ao coração, regulando assim o ritmo do batimento. (27)

O circuito eletrônico evidenciado na Fig. 17, é onde se encontra o conversor A/D do projeto do presente trabalho, é este que visa otimizar o seu funcionamento com a topologia  $\Sigma\Delta$ .

Figura 17 – Visualização do CAD explodido de um marca-passo. (11)

#### 2.4.3 Sinal de Eletrocardiograma (ECG)

A obtenção do sinal de eletrocardiograma (ECG) é um exame utilizando na medicina para inúmeras aplicações, uma delas, é a verificação do ritmo cardíaco, ou seja, analisar a periodicidade da onda gerada do registro da variação dos potenciais elétricos adquiridos pelo movimento do coração. O resultado da onda é demonstrado na Fig.18. (15)

Figura 18 – Formato de onda de um sinal de ECG.

O sinal do coração é obtido por meio de qualquer aparelho eletrocardiográfico, desde que, no mesmo, seja possível converter sinais analógicos em sinais digitais. Essa conversão deve ter uma resolução igual ou superior a 12 bits, e de forma ideal, uma taxa de amostragem de 250 Hz. (15)

Sendo assim, o uso de conversor do tipo  $\Sigma\Delta$  encaixa-se perfeitamente nesse processo de conversão, e promete devolver um sinal em ótima resolução. Ou seja, a implementação do conversor em um aparelho de marca passo conseguirá fazer seu papel de maneira ideal e com um baixo consumo de potência, uma vez que a resolução do  $\Sigma\Delta$  é alta.

### 3 DETALHAMENTO DO PROJETO

Este capítulo é delimitado ao detalhamento do conversor A/D do tipo Sigma-Delta  $(\Sigma\Delta)$  para o projeto de baixo consumo de potência que se aplique ao aparelho marca-passo. Uma vez que, para o projeto de um conversor é necessário conhecer seus parâmetros, a melhor escolha de modulação, e ainda, realizar testes que validem as escolhas.

Sendo assim, demonstra-se aqui, os parâmetros para o projeto deste conversor e análise de simulações de modulação de primeira e segunda ordem. Divide-se o conversor em duas etapas, a etapa analógica e a etapa digital que serão descritas nesse capítulo separadamente para o melhor entendimento das funções do conversor.

#### 3.1 Exposição do Motivo

O projeto necessita de um conversor de razoável resolução para a precisão do equipamento e também de um baixo consumo de potência. A escolha do conversor  $\Sigma\Delta$  se dá devido a utilização de baixa tensão, linearidade, rejeição de ruído à fonte de alimentação, ótima interface com o processador. Para um circuito integrado, em geral, é importante que existam poucos blocos analógicos, ou seja, que haja redução de blocos analógicos no sistema, o que ocorre no caso do conversor  $\Sigma\Delta$ . (28)

#### 3.2 Arquitetura e Funcionamento do Conversor $\Sigma\Delta$

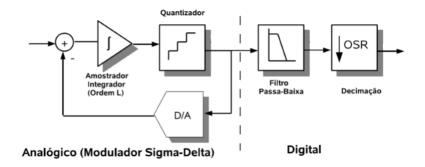

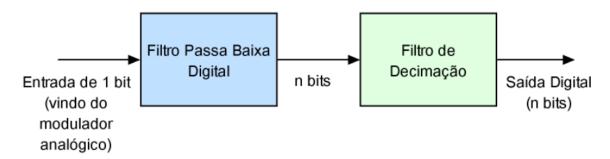

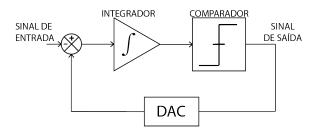

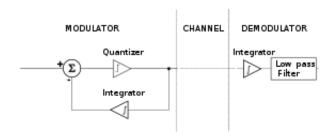

O conversor  $\Sigma\Delta$  é constituído por duas partes fundamentais: analógica e digital. A parte analógica é formada pelo modulador  $\Sigma\Delta$ , um integrador, um quantizador e um DAC e a parte digital é formada por um filtro digital (decimador), conforme o diagrama de blocos da Fig. 19.

Figura 19 – Diagrama de blocos de um  $\Sigma\Delta$ . (12)

A parte analógica que possui o modulador do tipo  $\Sigma\Delta$  recebe um sinal de entrada que se dirige ao modulador e ao integrador, sucessivamente. Em outras palavras, o erro entre o sinal amostrado e a saída do modulador é calculado para que seja integrado e quantizado.

O comparador comporta-se como um quantizador de 1 bit, assim, quando o sinal sai do comparador ele retorna à entrada via um DAC que define que a média do sinal que retorna seja igual ao sinal de entrada. Trabalha-se com uma técnica, noise-shaping, responsável por ejetar o ruído de quantização de baixas frequências em vertente a altas frequências.

Na parte digital, tem-se um decimador digital que é formado por um filtro passabaixa acompanhado de um downsampler, o qual tem a função de devolver o sinal à taxa de amostragem de Nyquist sem perda de informação, reduzindo assim a potência dos blocos ligados ao conversor A/D. (25)

O modelo da Figura 20, demonstra a explicação anterior e a arquitetura do conversor  $\Sigma\Delta$ , este nome dá-se ao fato de colocar o integrador Sigma antes do modulador, Delta.

Figura 20 – Arquitetura do conversor  $\Sigma\Delta$  (4)

Este tipo de modulação é considerado sobreamostrado, ou seja, trabalha muito acima da frequência de *Nyquist*. Sustenta uma modulação que pode ser mono-bit ou multi-bit e sua função de transferência adquirida da malha de realimentação varia até a ordem N. Contudo, se essa ordem for maior que 2, provavelmente, têm-se dificuldades com a estabilidade do sistema. (29)

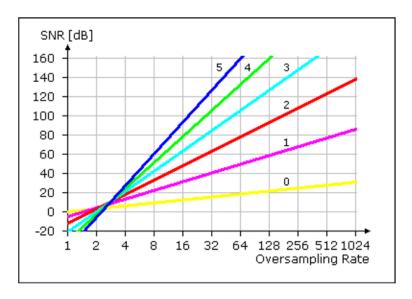

A ordem do sistema também está diretamente relacionada com a SNR, ou seja, quando se aumenta a ordem do modulador a taxa de amostragem diminui, conforme a Figura 21.

Figura 21 – Ordem do Modulador  $\Sigma\Delta$  e SNR x Taxa de amostragem (13)

Utilizando o teorema da superposição quando se tem uma entrada de ruído E(s)=0, a função de transferência do sinal pode ser descrita pela Eq. 3.1:

$$\frac{Y(s)}{X(s)} = \frac{\frac{1}{s}}{1 + \frac{1}{s}} = \frac{1}{s+1}$$

(3.1)

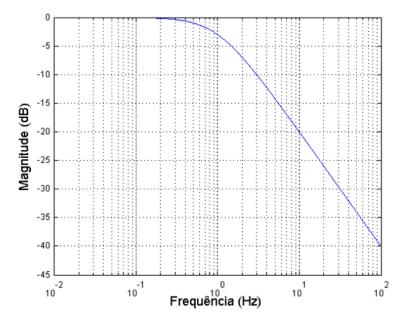

onde Y(s) é o sinal do modulador  $\Sigma\Delta$  e X(s) é o sinal de entrada, ambos no domínio da frequência. Isso retorna, desde que a frequência ultrapasse a frequência de corte do filtro passa baixa, o sinal pode ser reconstruído perfeitamente, conforme a Fig. 22.

Figura 22 – Comportamento das Funções de Transferência no modulador  $\Sigma\Delta$  utilizando um filtro passa-baixas.

Analogamente, pode-se encontrar a função de transferência para o ruído de quantização, basta igualar X(s)=0, de acordo com a Eq. 3.2:

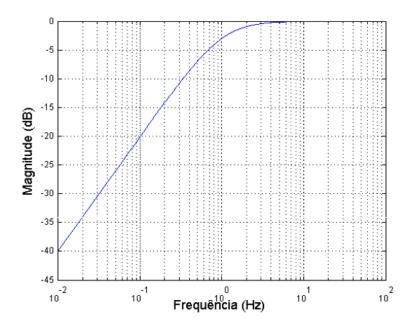

$$\frac{Y(s)}{E(s)} = \frac{1}{1 + \frac{1}{s}} = \frac{s}{s+1} \tag{3.2}$$

A equação demonstra que existe uma atenuação do ruído em baixas frequências tendo que eliminar o ruído excedente da banda de passagem e reduzir a taxa de amostragem com a inserção do decimador, o qual é um filtro passa-baixas, seguinte ao modulador. Conforme a Fig. 23.

Figura 23 – Comportamento das Funções de Transferência no modulador  $\Sigma\Delta$  utilizando um filtro passa-altas.

A respeito da estabilidade do sistema, tem-se a próxima seção 3.2.1 que utilizam o software MATLAB ® para validação de modulação de 1ª e 2ª ordem para a escolha do uso no projeto.

#### 3.2.1 Estabilidade dos Moduladores

A parte analógica compreende que estabilidade de um sistema é crucial na síntese de sistemas de controle realimentados, tornando-se um pré-requisito para projetos. No caso do modulador não é diferente, e para isso, assume-se uma análise dos moduladores de 1ª e 2ª ordem. A ordem do modulador  $\Sigma\Delta$  é determinada pelo seu número de integradores e é detalhada nas seções subsequentes.

#### 3.2.1.1 Modulador de 1ª Ordem

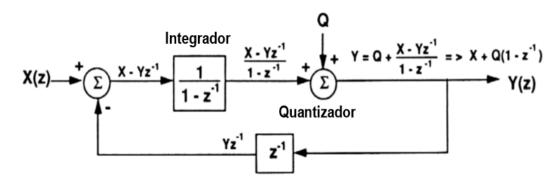

O modulador  $\Sigma\Delta$  mono-bit típico é aquele por densidade de pulso, isto é, a informação inserida é sobreamostrada em baixa resolução em amplitude e o filtro digital decimador é responsável pelo aumento da resolução em amplitude. Se a ordem do modulador é delimitada pelo número de integradores, então se há apenas um integrador tem-se, então, um modulador de ordem 1, conforme a Fig.24.

Figura 24 – Diagrama de Blocos de um modulador  $\Sigma\Delta$  de 1<sup>a</sup> ordem no domínio discreto (4)

A análise feita no domínio discreto, utilizando a transformada Z, é devido a facilidade de projeto de filtro de controle digitais, além de permitir que se transforme equações diferenciais em equações algébricas simplificadas. No plano z, encontra-se um círculo de raio R, o qual é centrado na origem, e possui uma região de convergência.

Analisando o diagrama de blocos, pode-se inferir a seguinte função de transferência na Eq. 3.3:

$$H(z) = b \cdot \frac{z^{-1}}{1 - z^{-1}} \tag{3.3}$$

Segundo a equação, o coeficiente "b" é ganho e serve como parâmetro para o ajuste pelo método do lugar geométrico das raízes (LGR). Utilizando a ferramenta rlocus(sys1) e sgrid do software MATLAB® pode-se plotar a Fig. 25 com uma entrada referente à uma entrada  $\frac{fs}{2}$  para z = -1 e o intervalo do LGR de z = 1 à z =  $\infty$ . Verifica-se na Figura 25, um sistema estável com b variando até o ponto 2 segundo o LGR. (28)

Figura 25 – Plotagem de LGR de 1ª ordem feita no software MATLAB com base teórica em FÁVERO(14)

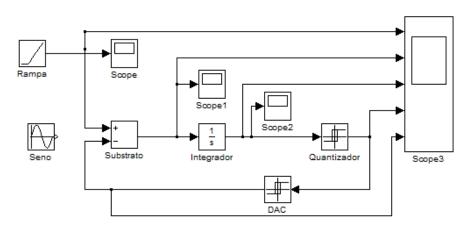

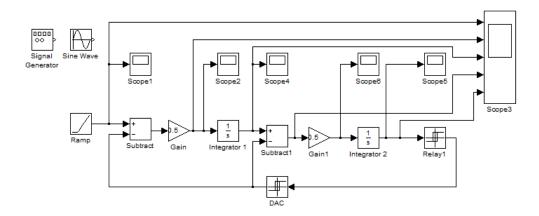

Para implementar e validar o modulador de 1ª ordem, usou-se a plataforma si-mulink do software MATLAB®, para criação de um diagrama de blocos, utilizando um modelo de referência SILVA(13), com entradas do tipo senoide e do tipo rampa conforme a Fig. 26. Esse diagrama, foi implementado obedecendo ao funcionamento de um modulador  $\Sigma\Delta$ . Apresentando um diferenciador que dobra a potência de ruído de quantização, contudo, apresenta um erro que é empurrado para altas frequências, fazendo assim, necessário o uso de filtro passa-baixas, para que esse, no processo de decimação, remova-o sem danos à resposta, observa-se que a parte digital (decimação) será descrita na seção 3.3.

Figura 26 – Diagrama de blocos de um modulador Sigma-Delta de 1ª ordem.

O diagrama de blocos apresenta uma entrada, podendo ser escolhida (rampa ou senoide), apresenta também um substrato, um integrador, um quantizador e um DAC, simulando o funcionamento de um modulador Sigma-Delta de primeira ordem, ou seja, com apenas um integrador.

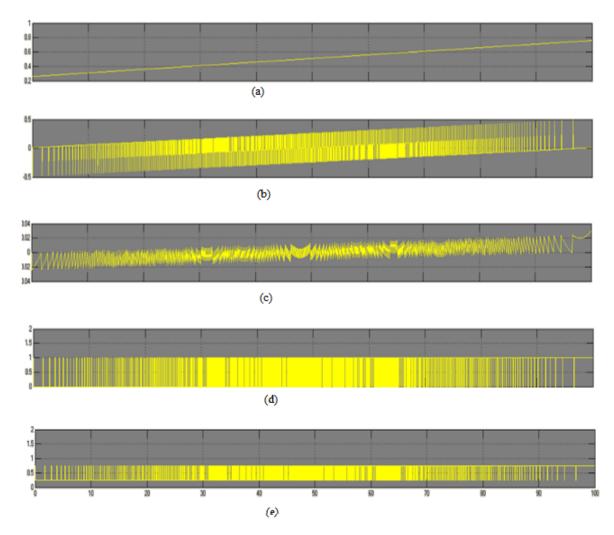

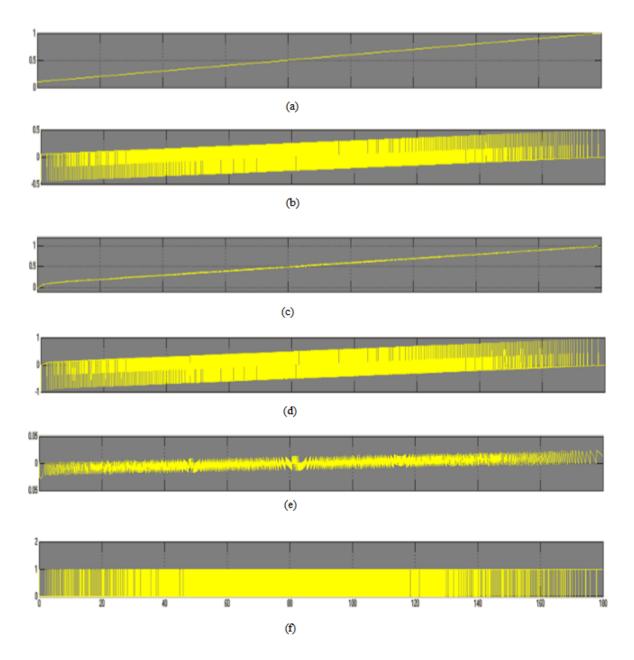

Para validação da simulação da Figura 26, utilizou-se como entrada uma função rampa com o valor inicial de 0.25V, e os valores de referências do DAC são de 0 à VDD contudo se usa  $\frac{1}{4}$ V e  $\frac{3}{4}$ V para manter a estabilidade. Uma vez que, utilizando esses valores, pode-se manter o DAC maior ou menor que o sinal, garantindo assim, a sua soma ou subtração. As formas de onda esperadas foram de sinal de entrada, diferenciador, integrador, quantizador e DAC, respectivamente na Fig. 27.

Figura 27 – Resposta modulador Sigma-Delta de 1ª ordem, com formas de ondas de sinal de (a) entrada, (b) diferenciador, (c) integrador, (d) quantizador, e (e) DAC.

É notório observar que os valores de referências de  $\frac{1}{4}$  Vdd e  $\frac{3}{4}$  Vdd são extremamente relevantes, pois é na faixa destes valores, que o modulador opera. Quando o sinal de entrada quase atinge o valor de referência mínimo, sendo menor que este, a saída do quantizador continua em zero até que esse sinal de entrada ultrapasse o valor de referência.

Ou modo seria quando o valor de referência está em seu valor máximo, neste caso, a saída do quantizador continua 1, ou seja, satura.

A partir da reposta simulada da Figura 27, nota-se que o diferenciador dobra a potência de ruído de quantização. Observa-se também, que o erro é jogado para frequências mais altas, que é uma característica da FFT, esta característica exige para sua remoção do erro o uso de um filtro e um decimador digital que serão evidenciados na seção 3.3. Levando em conta os parâmetros demonstrados no capitulo 2, a SNR de primeira ordem corresponde ao aumento de 9dB em cada incremento aplicado a taxa de sobreamostragem.

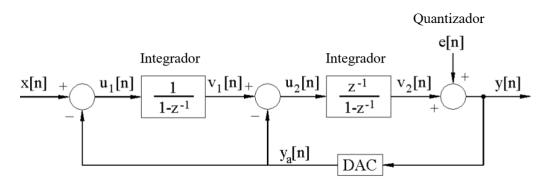

#### 3.2.1.2 Modulado de 2ª Ordem

O modulador  $\Sigma\Delta$  multi-bit é aquele de ordem maior que 1, ou seja, é um modulador de 1<sup>a</sup> ordem acrescido de mais um integrador, para se tornar de 2<sup>a</sup> ordem, e assim, sucessivamente. O modulador de 2<sup>a</sup> ordem necessita de uma taxa de amostragem menor para alcançar a mesma SNR que o de 1<sup>a</sup> ordem. Levando em conta essa vantagem, em relação ao anterior, demonstra-se esse modulador, conforme a Fig. 28.

Figura 28 – Diagrama de Blocos de um modulador  $\Sigma\Delta$  de 2ª ordem no domínio discreto (5)

Aproveitando o domínio Z e analisando o diagrama de blocos, pode-se inferir a seguinte função de transferência na Eq. 3.4:

$$H(z) = b \cdot \frac{2z - 1}{(z - 1)^2} \tag{3.4}$$

De maneira similar ao realizado na secção anterior, o coeficiente "b" é ganho e serve como parâmetro para o ajuste pelo LGR e pode-se plotar a Figura 29 com polo duplo em z = 1 e fim em z = 0.5 e z =  $\infty$ , respectivamente, referente a uma entrada equivalente a  $\frac{fs}{2}$ .

Figura 29 – Plotagem de LGR de 2ª ordem feita no software MATLAB com base teórica em FÁVERO(14)

Analogamente, para validar o modulador de 2ª ordem, usou-se a plataforma *simulink* do software MATLAB®, para criação de um diagrama de blocos modelo de referência SILVA(13), com entradas do tipo senoide e do tipo rampa conforme a Fig. 30.

Figura 30 – Diagrama de blocos de um modulador Sigma-Delta de 2ª ordem.

Para validação da simulação da Figura 30, utilizou-se os valores de referências iguais ao de 1ª ordem. As formas de onda esperadas foram de sinal entrada, diferenciador do 1º ganho, 1º integrador, diferenciador após o 2º ganho, 2º integrador e o quantizador, respectivamente na Fig. 31.

Figura 31 – Resposta modulador Sigma-Delta de 2ª ordem, com formas de ondas de sinal de entrada (a), diferenciador do 1º ganho (b), 1º integrador (c), diferenciador após o 2º ganho (d), 2º integrador (e) e o quantizador (f).

É notório observar que moduladores de ordem superior à três são considerados instáveis. Contudo com o uso do DAC de apenas 1 bit essa instabilidade é menor em relação aos de números de bits maiores. (28)