Instituto de Ciências Exatas Departamento de Ciência da Computação

## Projeto e Otimização de Circuitos Digitais por Técnicas de Evolução Artificial

Vitor Coimbra de Oliveira

Monografia apresentada como requisito parcial para conclusão do Bacharelado em Ciência da Computação

Orientador Prof. Dr. Marcus Vinicius Lamar

Brasília 2015

Universidade de Brasília — UnB Instituto de Ciências Exatas Departamento de Ciência da Computação Bacharelado em Ciência da Computação

Coordenador: Prof. Dr. Homero Luiz Piccolo

Banca examinadora composta por:

Prof. Dr. Marcus Vinicius Lamar (Orientador) — CIC/UnB

Prof. Dr. Ricardo Pezzuol Jacobi — CIC/UnB

Prof. Dr. Márcio da Costa Pereira Brandão — CIC/UnB

#### CIP — Catalogação Internacional na Publicação

Oliveira, Vitor Coimbra de.

Projeto e Otimização de Circuitos Digitais por Técnicas de Evolução Artificial / Vitor Coimbra de Oliveira. Brasília : UnB, 2015.

183 p. : il. ; 29,5 cm.

Monografia (Graduação) — Universidade de Brasília, Brasília, 2015.

1. algoritmo genético, 2. hardware evolutivo, 3. circuito digital, 4. cgp

CDU 004.4

Endereço: Universidade de Brasília

Campus Universitário Darcy Ribeiro — Asa Norte

CEP 70910-900

Brasília-DF — Brasil

Instituto de Ciências Exatas Departamento de Ciência da Computação

### Projeto e Otimização de Circuitos Digitais por Técnicas de Evolução Artificial

Vitor Coimbra de Oliveira

Monografia apresentada como requisito parcial para conclusão do Bacharelado em Ciência da Computação

Prof. Dr. Marcus Vinicius Lamar (Orientador)  ${\rm CIC/UnB}$

Prof. Dr. Ricardo Pezzuol Jacobi Prof. Dr. Márcio da Costa Pereira Brandão CIC/UnB CIC/UnB

Prof. Dr. Homero Luiz Piccolo Coordenador do Bacharelado em Ciência da Computação

Brasília, 02 de agosto de 2015

## Dedicatória

Dedico a meus pais, Marianita e Oswaldo, e meus irmãos, Artur e Luiza, que nunca deixaram de me apoiar.

# Agradecimentos

Agradeço ao meu orientador, Marcus Lamar, pelo grande apoio e suporte desde o princípio deste trabalho.

Agradeço também ao meu colega e amigo Matheus Pimenta por sua dedicação e interesse à área da computação.

## Resumo

Técnicas de projeto de circuitos digitais atualmente se baseiam principalmente em métodos top-down, que utilizam um conjunto de regras e restrições para auxiliar a construção do projeto. Por conta disso, ainda há um espaço desconhecido de soluções para vários problemas. Algoritmos genéticos, por outro lado, constroem soluções utilizando uma metodologia bottom-up, e provaram-se úteis para problemas de alta complexidade e de otimização.

Este trabalho propõe um novo algoritmo, denominado HMC-CGP, com convergência e otimização eficientes para problemas de síntese circuitos digitais. Em sua essência, esse algoritmo opera encontrando uma solução funcional utilizando a técnica MC-CGP e, em seguida, buscando otimizá-la utilizando CGP.

Os circuitos utilizados para testes foram somadores de 1 e 2 bits, multiplicador de 2 bits e decodificador para display de 7 segmentos. Os resultados observados mostram que o método converge mais rapidamente para uma resposta válida do que o método CGP convencional e atinge patamares de até 50% de redução para números de portas e transistores.

Palavras-chave: algoritmo genético, hardware evolutivo, circuito digital, cgp

## Abstract

Current digital circuit design techniques are based on top-down methods, which depend on a set of rules and restrictions made to help the design process. Because of that, there is still an unknown space of solutions for many problems. Genetic algorithms, on the other hand, build solutions by using a bottom-up methodology and have proven themselves useful for high complexity and optimization problems.

This work proposes a new algorithm, called HMC-CGP, for efficient convergence and optimization of digital circuit sintesis problems. In its essence, this algorithm first finds a functionally correct solution by making use of a technique called MC-CGP and, in its next phase, optimizes it by using another technique called CGP.

The circuits of the one and two bits adders, two bits multiplier and 7 segment display are used to verify the algorithm. The results show that the proposed algorithm converges faster to a functional circuit than the common CGP technique. The optimization phase was able to reduce gate and transistor counts by up to 50%.

**Keywords:** genetic algorithm, evolving hardware, digital circuit, cgp

# Sumário

| Li | sta d | le Figu              | ıras                                     | vii  |  |  |  |  |  |  |  |  |  |  |  |

|----|-------|----------------------|------------------------------------------|------|--|--|--|--|--|--|--|--|--|--|--|

| Li | sta d | le Tab               | elas                                     | ix   |  |  |  |  |  |  |  |  |  |  |  |

| Li | sta d | le Abr               | reviaturas e Siglas                      | xi   |  |  |  |  |  |  |  |  |  |  |  |

| 1  | Intr  | oduçã                |                                          | 1    |  |  |  |  |  |  |  |  |  |  |  |

|    | 1.1   | Objeti               | ivo Geral                                | . 2  |  |  |  |  |  |  |  |  |  |  |  |

|    | 1.2   | Objeti               | ivos Específicos                         | . 2  |  |  |  |  |  |  |  |  |  |  |  |

|    | 1.3   | Justifi              | icativa                                  | . 2  |  |  |  |  |  |  |  |  |  |  |  |

| 2  | Fun   | undamentação Teórica |                                          |      |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.1   | Álgeb                | ra Booleana                              | . 4  |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.1.1                | Operadores Básicos                       | . 4  |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.1.2                | Composição de Funções                    | . 5  |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.1.3                | Circuitos Combinacionais                 | . 5  |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.1.4                | Autossuficiência                         | . 10 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.1.5                | Forma Canônica                           | . 10 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.1.6                | Minimizando Funções Booleanas            | . 11 |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.2   | Lógica               | a Sequencial                             | . 13 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.2.1                | Elementos Básicos                        | . 13 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.2.2                | Máquina de Estados Finitos               | . 16 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.2.3                | Processo de <i>Design</i>                | . 19 |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.3   | Dispos               | sitivo Reconfigurável - FPGA             | . 20 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.1                | FPGA Altera Cyclone IV EP4CE115          | . 22 |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.4   | Algori               | itmos Genéticos                          | . 25 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.4.1                | Operadores Genéticos                     | . 25 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.4.2                | Operação de Seleção                      | . 26 |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.5   | Progra               | amação Genética Cartesiana               | . 28 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.5.1                | Forma Geral                              | . 29 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.5.2                | Restrição de Valores                     | . 30 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.5.3                | Estratégia evolucionária $(1 + \lambda)$ | . 31 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.5.4                | Neutralidade                             | . 32 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.5.5                | MC- $CGP$                                | . 32 |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.6   | Hardw                | vare Evolutivo                           | . 33 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.6.1                | Aplicações                               | . 33 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.6.2                | Formas de Evolução                       | . 34 |  |  |  |  |  |  |  |  |  |  |  |

| $\mathbf{R}$ | Referências 77 |         |                                           |            |  |  |  |  |

|--------------|----------------|---------|-------------------------------------------|------------|--|--|--|--|

| 5            | Con            | ıclusõe | ${f s}$                                   | <b>7</b> 5 |  |  |  |  |

|              | 4.3            | Otimiz  | zação a partir de técnicas clássicas      | 72         |  |  |  |  |

|              |                | 4.2.5   | Somador de 2 bits com carry               | 68         |  |  |  |  |

|              |                | 4.2.4   | Decodificador para display de 7 segmentos | 64         |  |  |  |  |

|              |                | 4.2.3   | Multiplicador de 2 bits                   | 60         |  |  |  |  |

|              |                | 4.2.2   | Somador de 2 bits                         | 57         |  |  |  |  |

|              |                | 4.2.1   | Somador completo de 1 bit com carry       | 54         |  |  |  |  |

|              | 4.2            | HMC-    | CGP                                       |            |  |  |  |  |

|              |                | 4.1.4   | Decodificador para display de 7 segmentos |            |  |  |  |  |

|              |                | 4.1.3   | Multiplicador de 2 bits                   |            |  |  |  |  |

|              |                | 4.1.2   | Somador de 2 bits                         | -          |  |  |  |  |

|              |                | 4.1.1   | Somador completo de 1 bit com carry       | _          |  |  |  |  |

| _            | 4.1            |         | e MC-CGP                                  | 46         |  |  |  |  |

| 4            | Res            | ultado  | s Obtidos                                 | 46         |  |  |  |  |

|              |                | 3.2.2   | Etapa 2: Otimização                       | 43         |  |  |  |  |

|              |                | 3.2.1   | Etapa 1: Solução funcional                | 43         |  |  |  |  |

|              | 3.2            | Algori  | tmo proposto                              | 42         |  |  |  |  |

|              |                | 3.1.3   | Simulação por software                    | 42         |  |  |  |  |

|              |                | 3.1.2   | Modelo em Verilog                         | 39         |  |  |  |  |

|              |                | 3.1.1   | Manipulação direta do Bitstream           | 38         |  |  |  |  |

|              | 3.1            | _       | ção do indivíduo                          | 38         |  |  |  |  |

| 3            | Met            | todolog | gia Proposta                              | 38         |  |  |  |  |

|              |                | 2.6.5   | Limitações em <i>Hardware</i> Evolutivo   | 37         |  |  |  |  |

|              |                | 2.6.4   | Níveis de Abstração e Granularidade       |            |  |  |  |  |

|              |                | 2.6.3   | Evoluindo Circuitos                       |            |  |  |  |  |

# Lista de Figuras

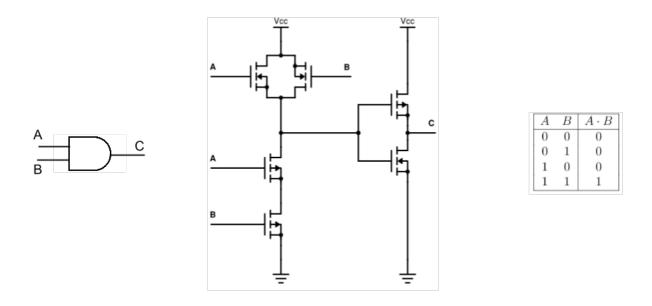

| 2.1  | Porta lógica AND, circuito e tabela verdade                                 | 6  |

|------|-----------------------------------------------------------------------------|----|

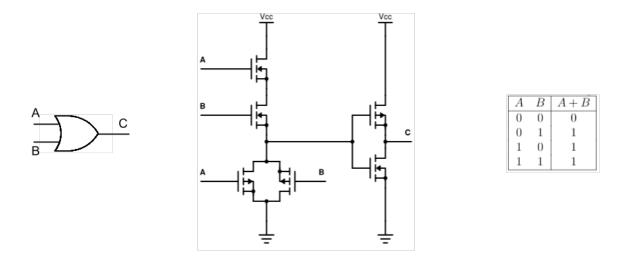

| 2.2  | Porta lógica OR, circuito e tabela verdade                                  | 6  |

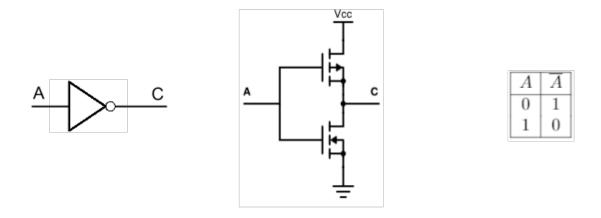

| 2.3  | Porta lógica $NOT$ , circuito e tabela verdade                              | 7  |

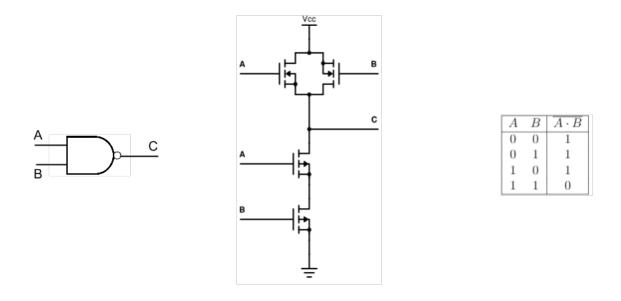

| 2.4  | Porta lógica <i>NAND</i> , circuito e tabela verdade                        | 7  |

| 2.5  | Porta lógica NOR, circuito e tabela verdade                                 | 8  |

| 2.6  | Porta lógica XOR, circuito e tabela verdade                                 | 8  |

| 2.7  | Porta lógica XNOR, circuito e tabela verdade                                | 9  |

| 2.8  | Circuito combinacional exemplificando tempo de propagação                   | 9  |

| 2.9  | Estrutura conceitual de uma máquina de estados                              | 14 |

| 2.10 | Estrutura realimentada estável independente de entradas (Tarnoff [2007]).   | 14 |

| 2.11 | Estrutura de retroalimentação utilizando portas NAND (Tarnoff [2007])       | 15 |

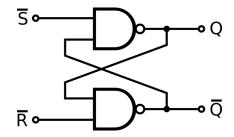

| 2.12 | Diagrama de um latch RS (Wikipedia [2014b])                                 | 15 |

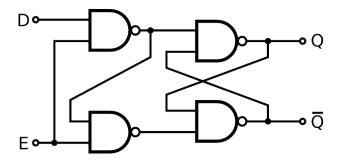

| 2.13 | Diagrama de um <i>latch</i> D (Wikipedia [2014b])                           | 16 |

| 2.14 | Diagrama de um flip-flop D (Wikipedia [2014b])                              | 16 |

| 2.15 | Exemplo de Diagrama de Transições e Estados (Belgasem [2003])               | 17 |

| 2.16 | Exemplo de Diagrama de Transições e Estados utilizando o paradigma de       |    |

|      | Moore                                                                       | 18 |

| 2.17 | Processo de projeto de um circuito sequencial (Belgasem [2003])             | 19 |

| 2.18 | Configuração de memória mapeando para um circuito em um dispositivo         |    |

|      | reconfigurável (Torresen [2004])                                            | 21 |

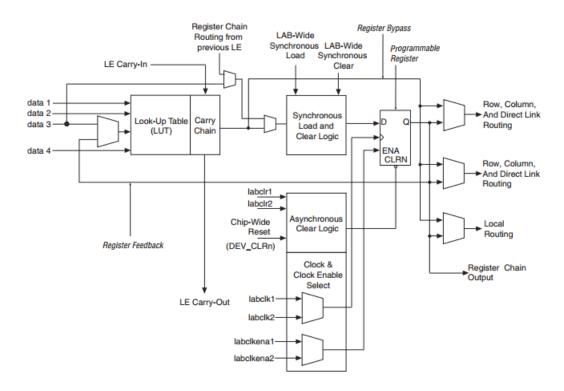

|      | Logic Element (LE) da família de FPGAs Cyclone II (Altera [2007])           | 21 |

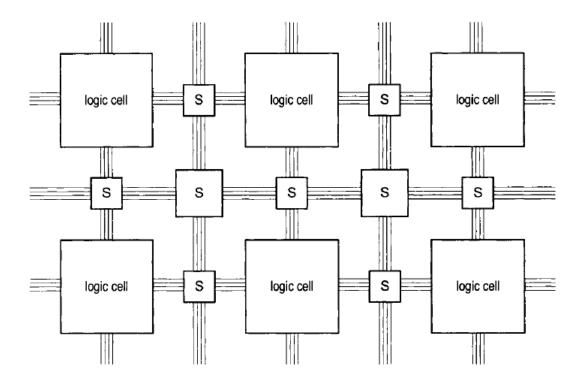

|      | Arranjo conceitual de elementos lógicos e chaves programáveis (Chu [2008]). | 22 |

| 2.21 | LE da família de FPGAs Cyclone IV (Altera [2013])                           | 23 |

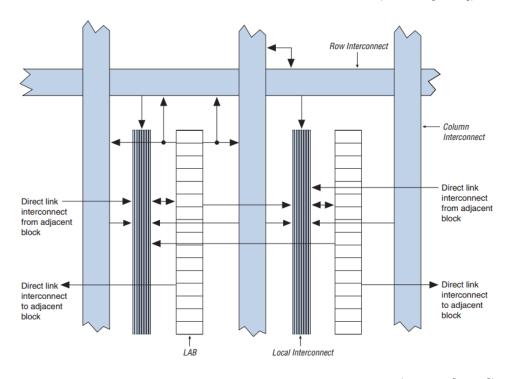

|      | LAB com barramento de interconexão local (Altera [2013])                    | 23 |

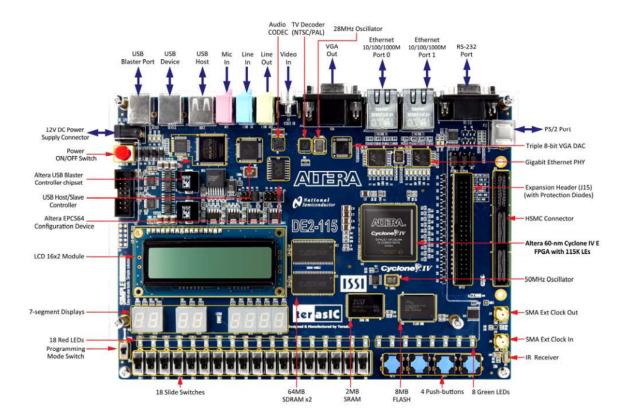

|      | Layout da placa de desenvolvimento Altera DE2-115 (Altera [2010])           | 24 |

|      | Etapas típicas de compilação para bitstream alvo                            | 25 |

|      | Exemplo de crossover entre dois cromossomos (Wikipedia [2014a])             | 26 |

|      | Passos gerais para um algoritmo genético.                                   | 27 |

|      | Exemplo da seleção por roleta (Wikipedia [2014c])                           | 27 |

|      | Forma geral da estrutura de um sistema genético cartesiano (Miller [2011]). | 29 |

| 2.29 | Exemplo de sistema cartesiano genético. Evidencia relação entre genótipo    |    |

|      | e fenótipo (Miller [1999])                                                  | 30 |

|      | Exemplo de execução do algoritmo $(1 + \lambda)$                            | 31 |

| 2.31 | Exemplo exibindo comportamento isolado de cada cromossomo em um am-         |    |

|      | biente MC-CGP (Walker et al. [2009])                                        | 32 |

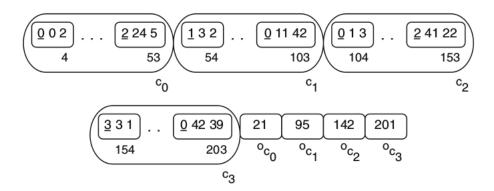

|      | Espaço de soluções e alcances das abordagens evolutiva e humana             | 34 |

| 2.33 | Ciclo geral da evolução de circuitos intrînsecos (Thompson [1998])          | 35 |

| 2.34 | Bentley [2002])                                                               | 36 |

|------|-------------------------------------------------------------------------------|----|

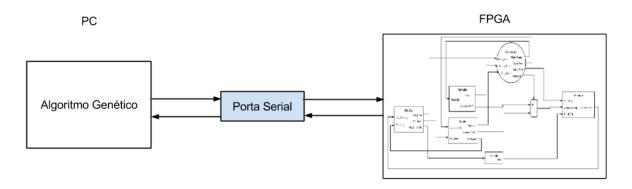

| 3.1  | Visão de alto nível da comunicação de dados                                   | 39 |

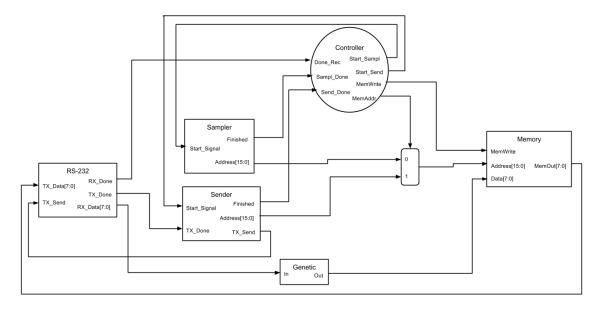

| 3.2  | Caminho de dados do circuito de interface                                     | 39 |

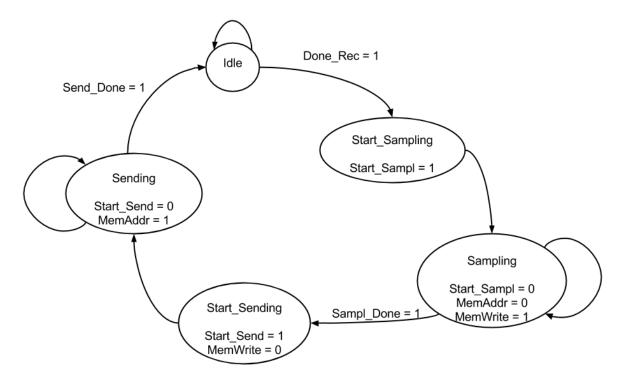

| 3.3  | Máquina de estados do circuito que gerencia a comunicação entre o com-        |    |

|      | putador e o FPGA                                                              | 40 |

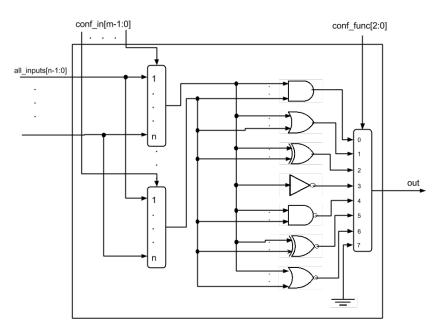

| 3.4  | Elemento lógico básico que compõe a grade do circuito virtual reconfigurável. | 41 |

| 3.5  | Visão geral do algoritmo HMC-CGP                                              | 44 |

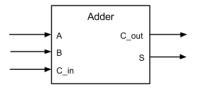

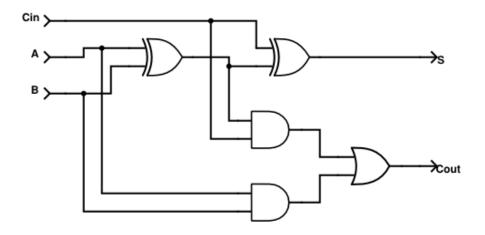

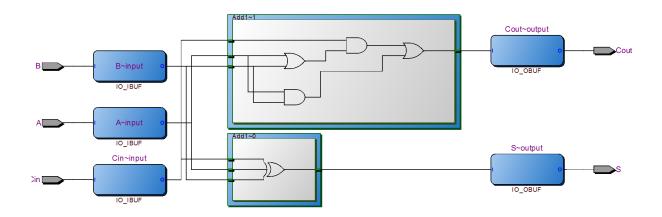

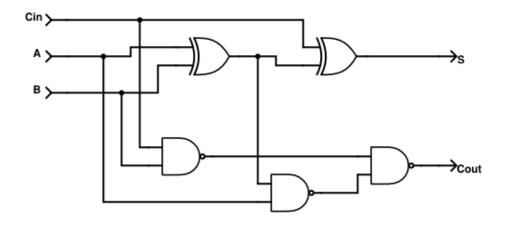

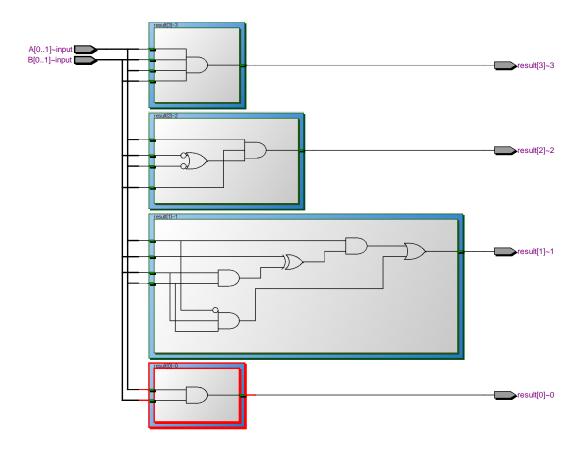

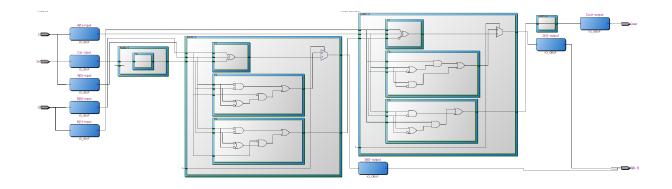

| 4.1  | Módulo somador de 1 bit com carry-in                                          | 47 |

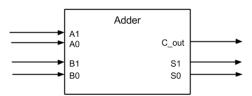

| 4.2  | Módulo somador de 2 bits                                                      | 48 |

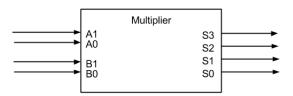

| 4.3  | Módulo multiplicador de 2 bits                                                | 49 |

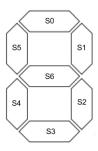

| 4.4  | Associação das saídas aos LEDs de um display de 7 segmentos                   | 52 |

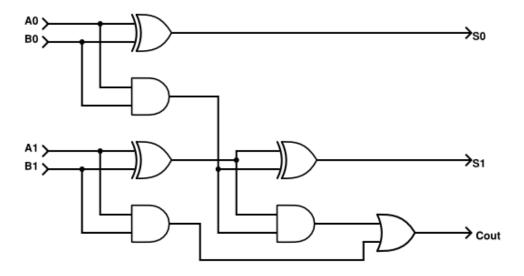

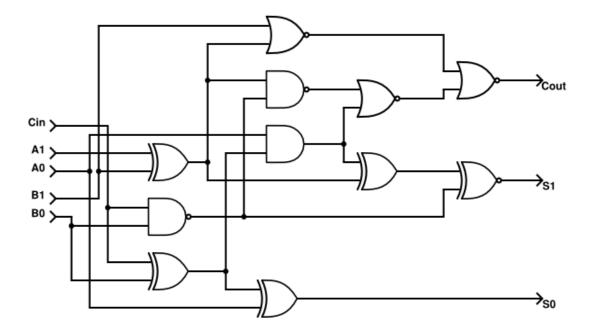

| 4.5  | Somador completo de 1 bit clássico                                            | 54 |

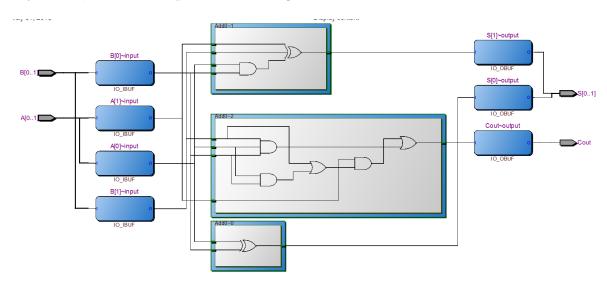

| 4.6  | Somador completo de 1 bit sintetizado pelo software Quartus II                | 55 |

| 4.7  | Exemplo de solução encontrada pelo HMC-CGP para o circuito somador            |    |

|      | de 1 <i>bit.</i>                                                              | 57 |

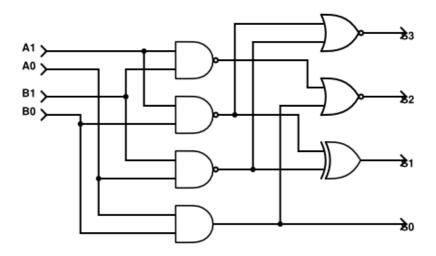

| 4.8  | Somador de 2 bits como normalmente projetado                                  | 58 |

| 4.9  | Somador de 2 bits projetado pelo Quartus II                                   | 58 |

| 4.10 | 1 3 1                                                                         | 60 |

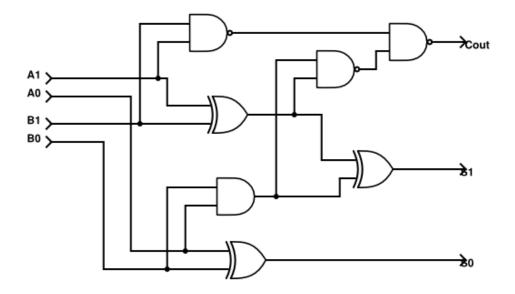

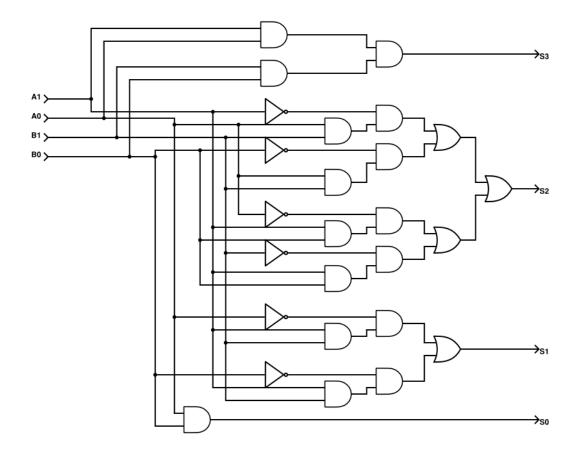

|      | Multiplicador de 2 bits gerado por minimização por Mapa de Karnaugh           | 61 |

|      | Circuito multiplicador de 2 bits sintetizado pelo Quartus II                  | 62 |

|      | Multiplicador de 2 bits obtido pelo HMC-CGP                                   | 64 |

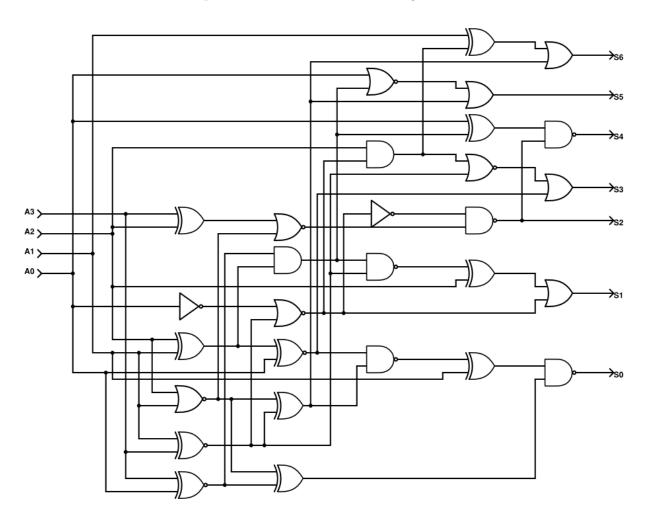

| 4.14 | Circuito decodificador para display de 7 segmentos com 29 portas, 5 cama-     |    |

|      | das e 152 transistores obtido pelo HMC-CGP                                    | 66 |

|      | Circuito gerado por síntese pelo software Quartus II.                         | 67 |

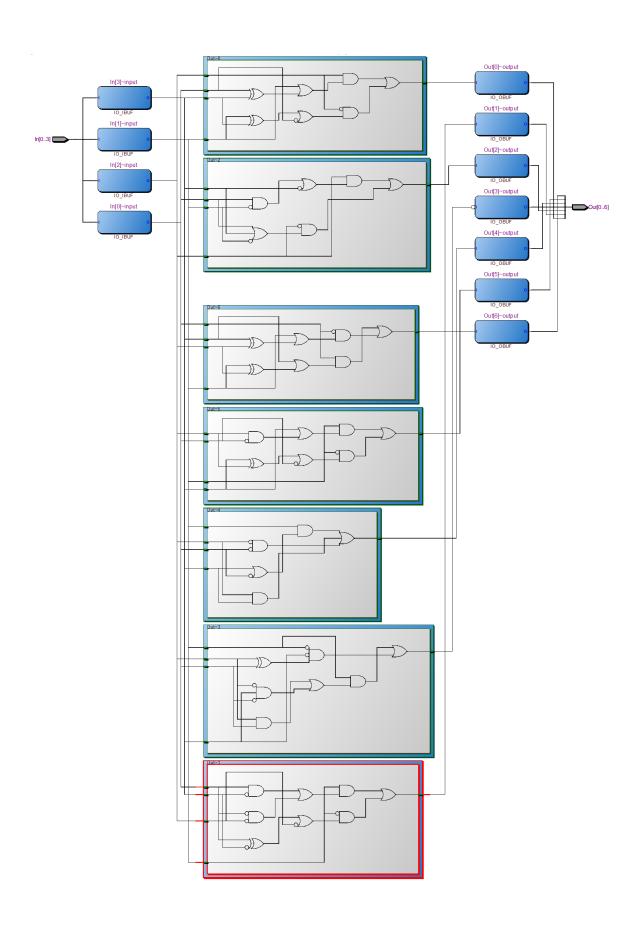

|      | Circuito somador de 2 bits com carry sintetizado por Quartus II               | 70 |

| 4.17 | Circuito mais otimizado encontrado em termos de $n_c$ para somador de 2       |    |

|      | bits com carry pelo HMC-CGP                                                   | 72 |

# Lista de Tabelas

| 2.1  | Tabela verdade da função $f(A,B) = \overline{A} \cdot \overline{B} + A \cdot B$                                                          | 5  |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Tabela verdade com mini-termos da função canônica $f(A, B, C) = A \cdot B$ .                                                             |    |

|      | $\overline{C} + \overline{A} \cdot \overline{B} \cdot \overline{C}$                                                                      | 11 |

| 2.3  | Tabela verdade com mini-termos da função $f(A,B,C) = \overline{A} \cdot B \cdot C + \overline{A} \cdot \overline{B}$ .                   |    |

|      | $C + A \cdot \overline{B} \cdot C$                                                                                                       | 11 |

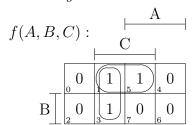

| 2.4  | Mapa de Karnaugh de $f(A, B, C) = \overline{A} \cdot B \cdot C + \overline{A} \cdot \overline{B} \cdot C + A \cdot \overline{B} \cdot C$ | 12 |

| 2.5  | Mapa de Karnaugh exibindo células passíveis de otimização                                                                                | 12 |

| 2.6  | Tabela de implicantes primos para a função $\sum m(1,3,5)$                                                                               | 13 |

| 2.7  | Gráfico de implicantes primos para a função $\sum m(1,3,5)$ . Construído após                                                            |    |

|      | o primeiro passo do algoritmo de Quine-McCluskey                                                                                         | 13 |

| 2.8  | Tabela verdade da estrutura <i>latch</i> D                                                                                               | 16 |

| 2.9  | Tabela verdade do flip-flop tipo D                                                                                                       | 16 |

| 2.10 | Exemplo de tabela de transição de estados                                                                                                | 18 |

|      | Tabela de transições de estados para o exemplo utilizando o paradigma de                                                                 |    |

|      | Moore                                                                                                                                    | 19 |

| 2.12 | Exemplo de operação de mutação em um cromossomo                                                                                          | 26 |

|      |                                                                                                                                          |    |

| 4.1  | Tabela verdade para o circuito somador de 1 bit                                                                                          | 47 |

| 4.2  | Resultados para somador de 1 bit com carry-in                                                                                            | 48 |

| 4.3  | Tabela verdade para o somador de 2 bits                                                                                                  | 49 |

| 4.4  | Resultados para o somador de 2 bits                                                                                                      | 49 |

| 4.5  | Tabela verdade para o multiplicador de 2 bits                                                                                            | 50 |

| 4.6  | Resultados para o multiplicador de 2 bits                                                                                                | 50 |

| 4.7  | Dígitos representados por codificação BCD                                                                                                | 51 |

| 4.8  | Dígitos superiores na codificação hexadecimal                                                                                            | 51 |

| 4.9  | Tabela verdade para o decodificador display de 7 segmentos hexadecimal                                                                   | 52 |

| 4.10 | Resultados para o decodificador display de 7 segmentos hexadecimal                                                                       | 52 |

| 4.11 | Tabela de funções lógicas e número de transistores                                                                                       | 54 |

| 4.12 | Resultados dos experimentos realizados para o somador completo de 1 bit.                                                                 | 56 |

| 4.13 | Resultados dos experimentos realizados para o somador de 2 bits                                                                          | 59 |

| 4.14 | Resultados dos experimentos realizados para multiplicador de 2 bits                                                                      | 63 |

| 4.15 | Resultados dos experimentos realizados para decodificador para display de                                                                |    |

|      | 7 segmentos hexadecimal.                                                                                                                 | 65 |

| 4.16 | Tabela verdade para o módulo somador de 2 bits com carry                                                                                 | 69 |

|      | Resultados dos experimentos realizados para o somador de 2 bits com carry.                                                               | 71 |

|      | Resultados dos experimentos realizados para o somador completo de 1 bit                                                                  |    |

|      | com <i>carry</i> gerado por Mapa de <i>Karnauah</i>                                                                                      | 73 |

## Lista de Abreviaturas e Siglas

```

ASIC Application-Specific Integrated Circuit. 19

BCD Binary Coded Decimal. 50

CGP Cartesian Genetic Programming. iii, iv, 2, 27, 29–31, 36, 41–43, 45–49, 51, 52, 65,

73, 74

CPU Central Processing Unit. 45

DNA Acido Desoxirribonucleico. 1

EEPROM Electrically Erasable Programmable Read-Only Memory. 23

FPGA Field-Programmable Gate Array. 1–4, 19–21, 23, 33, 35–37, 39–41, 45, 67, 74, 75

FPL Field-Programmable Logic. 20

HDL Hardware Description Language. 19, 34

HMC-CGP Hybrid Multi-Chromosome Cartesian Genetic Programming. iii, iv, 2, 3,

41–45, 52, 54, 56, 58, 59, 63, 65, 71, 73–75

I/O Input / Output. 19, 21

LAB Logic Array Block. 21, 22

LE Logic Element. 20, 21, 67

LED Light emitter diode. 23, 51

LUT Look-up Table. 19, 21

MC-CGP Multi-Chromosome Cartesian Genetic Programming. iii, iv, 2, 31, 36, 41, 42,

45–49, 52, 65, 72–74

PC Personal Computer. 75

PLL Phase Locked Loop. 21

```

RAM Random Access Memory. 45

SDRAM Synchronous Dynamic Random Access Memory. 23

SRAM Synchronous Random Access Memory. 23

${f tpd}$  propagation delay time.  ${f 5}$

USB Universal Serial Bus. 23, 75

## Capítulo 1

## Introdução

Tradicionalmente, os seres humanos projetam sistemas de alta complexidade, tais como prédios, computadores e carros, utilizando um conjunto complexo de regras que visam cumprir uma série de requerimentos. Por natureza, esse processo é feito de uma sistemática top-down, ou seja, se parte de uma especificação abstrata do problema e segue-se através da construção de sistemas menores e mais específicos. Esta sistemática se apresenta em forte contraste com o mecanismo que resultou na concepção da imensa diversidade de seres vivos hoje encontrados. Os seres vivos são a consequência de um conjunto de instruções simples, codificadas por DNA, que constroem componentes mais complexos. Um organismo é criado após inúmeras reações químicas causadas pelo DNA. Organismos complexos são então formados através de um processo evolutivo. Segundo Darwin (Darwin [1859]), uma das bases da evolução é o mecanismo de Seleção Natural. Este mecanismo é baseado em uma população composta de diversos indivíduos, cada um com características próprias definidas pelos genes. A sobrevivência de um indivíduo e sua capacidade de transferir seus genes para seus descendentes são diretamente relacionados à sua adaptação em relação ao ambiente em que se encontra.

Com o advento da computação, diversas técnicas para design de componentes digitais para auxiliar esse evento e solucionar diferentes problemas surgiram nos últimos anos.

Dentre eles, surgiram os chamados dispositivos reconfiguráveis, cuja principal característica é a sua capacidade de ser configurado para a realização de tarefas específicas. Alguns desses dispositivos podem ter partes reconfiguradas enquanto outras estão executando suas funções. Um tipo especial de circuito reconfigurável chamado Field-Programmable Gate Array (FPGA) é utilizado neste trabalho.

Formado essencialmente por uma grade de células lógicas, cada qual interconectada com suas vizinhas e cujo objetivo é controlar se dois fios estão eletricamente ligados ou não, torna-se possível a implementação de um vasto conjunto de funções Booleanas (Garcia et al. [2006]).

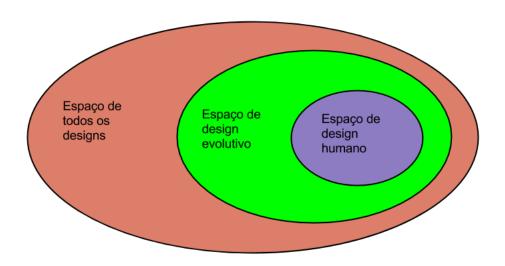

Paralelamente, outra maneira de solução de problemas, chamada de *Programação Genética*, baseada em algoritmos genéticos, já vem há muito tempo sendo utilizada para problemas relacionados a *software*. Algoritmos genéticos se baseiam fortemente nos princípios da seleção natural para resolução de problemas (Melanie [1999]). Os indivíduos de uma população representam as possíveis soluções e são codificados em uma sequência de *bits* chamada *bitstream*, atuando com o papel de cromossomos, descrevendo essa solução. Novas populações são formadas e testadas utilizando a chamada função de *fitness*, em

que cada indivíduo é avaliado e associado a um score baseado no quão perto do resultado desejado ele chegou. Esse score determina suas chances de se reproduzirem e passarem seus cromossomos para as populações seguintes (Melanie [1999]). Dessa maneira, à medida que novas iterações são feitas, indivíduos pouco adaptados tendem a não sobreviver e os mais adaptados a se reproduzir. Ao longo do tempo, devido aos mecanismos de crossover e mutação geralmente encontrados em tais algoritmos, pequenas modificações podem ser observadas, resultando em novas soluções e possivelmente gerando também um aumento no fitness da população e, consequentemente, uma aproximação maior à solução adequada.

A motivação principal deste trabalho foi a união dos dois campos apresentados e possivelmente a exploração de um espaço de soluções ainda não bem explorado. A utilização de ambas as técnicas pode ser aplicada tanto a circuitos digitais quanto analógicos (Burian [2009]). Neste trabalho serão explorados apenas a aplicação de algoritmos genéticos a circuitos digitais.

### 1.1 Objetivo Geral

Este trabalho possui como objetivo principal o estudo e implementação de técnicas de evolução genética no projeto de circuitos digitais combinacionais e sequenciais em FPGA.

### 1.2 Objetivos Específicos

De forma a verificar a eficácia da abordagem genética a projetos de circuitos digitais, as seguintes metas foram estabelecidas:

- Implementar os algoritmos CGP e MC-CGP, comumente utilizados para a evolução de circuitos digitais;

- Projetar os circuitos a serem avaliados: somadores de 1 e 2 bits, multiplicador de 2 bits e display de 7 segmentos;

- Propor uma nova estratégia evolutiva HMC-CGP;

- Mostrar a eficácia do método proposto por meio de comparação dos resultados nos circuitos projetados.

#### 1.3 Justificativa

Thompson [1998] mostra que esse tipo de abordagem oferece algumas vantagens interessantes quando se utiliza um hardware reconfigurável como uma FPGA. O fato de ser reconfigurável torna viável a rápida execução de diferentes circuitos, permitindo a flexibilidade necessária normalmente exigida em algoritmos evolucionários. Das vantagens mencionadas, algumas são: um ambiente mais rico proveniente da falta de restrições usualmente aplicadas para a conveniência de designers e, por consequência, o aproveitamento de características sutis da física dos semicondutores dos componentes. Como resultado

disso, circuitos então evoluídos geneticamente podem apresentar melhor uso da área oferecida, menor gasto de energia e maior eficiência na execução da tarefa dada quando comparados a circuitos feitos utilizando o método de projeto convencional.

Este trabalho está organizado da seguinte forma: no capítulo 2 é apresentada a revisão bibliográfica sobre os conceitos de álgebra booleana, circuitos digitais, FPGAs e algoritmos genéticos e suas abordagens. O capítulo 3 apresenta um detalhamento sobre a metodologia utilizada e desenvolvimento da proposta de evolução HMC-CGP. No capítulo 4 são mostrados os resultados obtidos pela aplicação da metodologia proposta. Finalmente, o capítulo 5 apresenta as conclusões e trabalhos futuros.

## Capítulo 2

## Fundamentação Teórica

Este capítulo apresentará conceitos básicos utilizados neste trabalho. Primeiramente, serão mostrados os fundamentos da Álgebra Booleana, juntamente com técnicas de otimização de expressões lógicas. Uma breve explicação sobre os dispositivos FPGAs é dada, em seguida, e, por último, é feita uma revisão sobre a base teórica de algoritmos genéticos.

## 2.1 Álgebra Booleana

Inicialmente proposta por George Boole (Nelson et al. [1995]), a área hoje denominada Álgebra Booleana trata de problemas relacionados à lógica moderna. Essa lógica também forma a base para computação em sistemas modernos. Qualquer algoritmo ou circuito eletrônico digital pode ser representado por um sistema de equações booleanas (Hyde [2001]).

Nesta álgebra, variáveis assumem apenas um conjunto finito de valores. Mais precisamente, apenas dois valores distintos são representados:  $\{0,1\}$ . Operações são realizadas sobre essas variáveis utilizando operadores unários, que possuem uma variável como entrada, e binários, que possuem duas.

### 2.1.1 Operadores Básicos

As funções básicas e principais que compõem todas as outras possíveis são denominadas: *AND*, *OR* e *NOT*, formando então um conjunto completo de conectivos.

#### Operador AND

O resultado da operação AND pode ser definido como 1 apenas se ambas as entradas são 1 e 0 senão. Essa operação normalmente é representada utilizando o símbolo  $\cdot$  e sua tabela verdade é mostrada na figura 2.1.

#### Operador OR

O operador OR tem como sua saída 1 se quaisquer das entradas for 1, senão é definida como 0. Sua tabela verdade pode ser escrita conforme mostra a tabela na figura 2.2. Associa-se a este operador o símbolo +.

#### Operador NOT

A operação NOT é a simples inversão do valor passado. Portanto, se sua entrada for 1, a saída é 0 e vice-versa como mostra a tabela na figura 2.3. Se uma variável é denominada A, então sua inversão é definida como  $\overline{A}$ .

#### 2.1.2 Composição de Funções

Funções em Álgebra Booleana são criadas a partir de composições utilizando os três operadores básicos apresentados interespaçados pelas constantes 0, 1 ou variáveis. Um exemplo de função seria  $f(A,B) = A \cdot \overline{B} + \overline{A} \cdot B$  cujo resultado se limita ao conjunto  $\{0,1\}$ . Por consequência, uma característica favorável é conseguir representar essas funções a partir de tabelas verdade, como mostra a tabela 2.1 para a função descrita. Essa função também é conhecida como o operador XOR (eXclusive OR) binário.

Tabela 2.1: Tabela verdade da função  $f(A, B) = \overline{A} \cdot \overline{B} + A \cdot B$

|   | 3 - 3 ( ) ) |                |                |                        |                        |                                               |  |  |  |  |

|---|-------------|----------------|----------------|------------------------|------------------------|-----------------------------------------------|--|--|--|--|

| A | B           | $\overline{A}$ | $\overline{B}$ | $A \cdot \overline{B}$ | $\overline{A} \cdot B$ | $A \cdot \overline{B} + \overline{A} \cdot B$ |  |  |  |  |

| 0 | 0           | 1              | 1              | 0                      | 0                      | 0                                             |  |  |  |  |

| 0 | 1           | 1              | 0              | 0                      | 1                      | 1                                             |  |  |  |  |

| 1 | 0           | 0              | 1              | 1                      | 0                      | 1                                             |  |  |  |  |

| 1 | 1           | 0              | 0              | 0                      | 0                      | 0                                             |  |  |  |  |

#### 2.1.3 Circuitos Combinacionais

Outra maneira de representar funções booleanas é por meio de portas lógicas. Atualmente, circuitos digitais combinacionais, ou seja, aqueles cujas saídas dependem exclusivamente de suas entradas, são abstraídos dessa forma.

#### Representação física

Fisicamente, portas lógicas são implementadas utilizando-se elementos básicos de circuitos elétricos, como resistores, diodos e transistores (Agarwal and Lang [2005]). O nível lógico 1 é considerado como aproximadamente 5V de tensão, e para cerca de 0V, considera-se como o nível lógico 0.

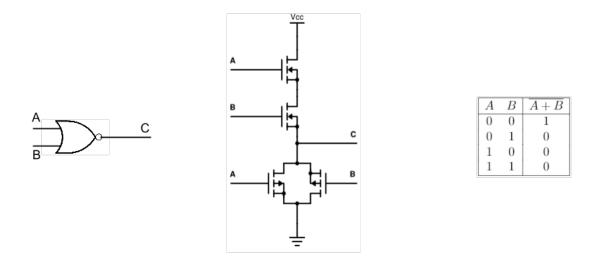

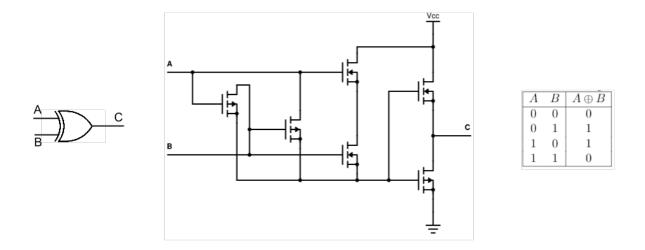

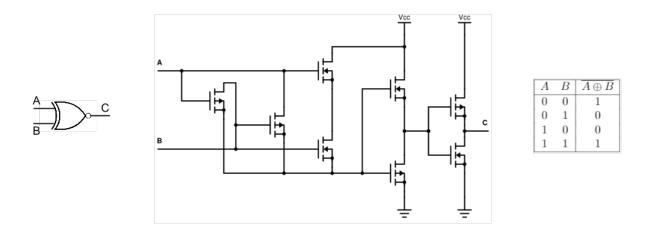

Utilizando as variáveis A e B para entradas e C para saída, as figuras fig. 2.1, fig. 2.2, fig. 2.3, fig. 2.4, fig. 2.5, fig. 2.6, fig. 2.7 mostram os símbolos das portas lógicas, uma possível construção física utilizando transistores bipolares e suas respectivas tabelas verdade.

Figura 2.1: Porta lógica AND, circuito e tabela verdade.

Figura 2.2: Porta lógica OR, circuito e tabela verdade.

Figura 2.3: Porta lógica NOT, circuito e tabela verdade.

Figura 2.4: Porta lógica NAND, circuito e tabela verdade.

Figura 2.5: Porta lógica NOR, circuito e tabela verdade.

Figura 2.6: Porta lógica XOR, circuito e tabela verdade.

Figura 2.7: Porta lógica XNOR, circuito e tabela verdade.

Observa-se que, dependendo da porta lógica, a sua implementação pode requerer diferentes números de transistores, sendo que a porta NOT a mais simples, e as portas XOR e XNOR as mais complexas.

#### Tempo de propagação

Enquanto expressões booleanas são suficientes para expressar a funcionalidade de circuitos digitais combinacionais, uma característica importante para designs mais complexos é o tempo de propagação propagation delay time (tpd). Ele pode ser definido como o tempo necessário para que, após uma mudança na entrada do circuito, a saída se estabilize, ou seja se torne válido, em 0 ou 1 (Agarwal and Lang [2005]).

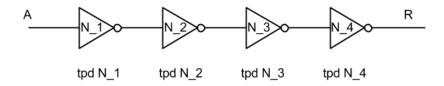

Como exemplo, uma mudança na entrada A do circuito da figura 2.8 terá seu resultado refletido na saída R somente após a propagação do sinal estável em cada uma das portas lógicas NOT, resultando em um tempo de propagação total de:

$$tpd_{total} = tpd_{N_1} + tpd_{N_2} + tpd_{N_3} + tpd_{N_4}$$

Figura 2.8: Circuito combinacional exemplificando tempo de propagação.

Deste modo, quanto mais camadas de portas lógicas são necessárias para a tarefa desejada, maior será o atraso para a obtenção da resposta, limitando assim a máxima frequência de utilização do circuito.

Tipicamente, fios possuem aproximadamente um atraso de 1ns para cada 15cm de comprimento, enquanto uma porta lógica pode variar de cerca de 10ns até à casa de picossegundos, dependendo da tecnologia utilizada (Balch [2003]).

#### 2.1.4 Autossuficiência

Autossuficiência para o caso de portas lógicas significa que é possível formar qualquer função booleana com uma combinação delas. Para isto, basta mostrar que é possível que sejam geradas as portas AND, OR e NOT, que compõem um dos conjuntos completos de operações, a partir de uma única porta lógica. Se isso for verdade, então, já que se pode representar todas as funções booleanas com apenas essas 3 funções (Nelson et al. [1995]), a porta lógica em questão também o faz. Esse tipo de característica também é conhecido como porta lógica universal.

É o caso da função NAND, funcionalmente idêntica a  $f(A,B) = \overline{A \cdot B}$ . Sua tabela verdade pode ser vista na tabela da figura 2.4. O operador NOT é reproduzido a partir da função de apenas NANDs como  $f(A) = \overline{A \cdot A}$ . A função OR pode ser defininida como  $g(A,B) = \overline{\overline{A \cdot A} \cdot \overline{B \cdot B}}$ . Para AND, define-se  $h(A,B) = \overline{\overline{A \cdot B} \cdot \overline{A \cdot B}}$ .

Outro exemplo é o da função NOR (tabela verdade na figura 2.5). Sua representação em funções booleanas se dá por uma porta OR seguida de uma NOT,  $f(A,B) = \overline{A+B}$ . Para mostrar que NOR também possui essa completude funcional, sua representação para portas OR se dá como  $\overline{A+B}+\overline{A+B}$ . Para portas AND,  $\overline{A+A}+\overline{B+B}$  e, NOT,  $\overline{A+A}$ .

Portas *NAND* e *NOR* são desejáveis não só por serem funcionalmente completas, mas também por sua facilidade de fabricação quando comparadas a outras portas lógicas. Como consequência, elas são utilizadas no conjunto das portas básicas em muitas famílias de *IC*s de lógica digital (Mano [2006]).

#### 2.1.5 Forma Canônica

A criação de funções booleanas se mostra ser bastante flexível e diversificada. Porém, nem todas são únicas. É possível que duas funções distintas produzam a mesma saída, como por exemplo  $f(A,B) = A \cdot B$  e  $g(A,B) = \overline{\overline{A} + \overline{B}}$ .

Neste caso, há uma infinidade de funções booleanas para uma dada tabela verdade. Torna-se necessário uma padronização visando apenas uma função booleana possível para cada configuração de tabela verdade.

Isto pode ser alcançado utilizando-se de formas canônicas de expressões lógicas. Há duas formas principais de para expressões canônicas, conhecidas como a forma soma de produtos e a forma produto de somas (Agarwal and Lang [2005]). A forma de utilização mais comum é o formato de soma de produtos, também chamado de soma de mini-termos.

Para um circuito com entradas  $A_1, A_2, \ldots, A_n$ , um mini-termo é um produto em que cada variável de entrada ou seu complemento aparecem apenas uma vez (Nelson et al. [1995]). Para um circuito com entradas  $A, B, C \in D$ , um mini-termo possível é  $A \cdot B \cdot \overline{C} \cdot D$ , enquanto que  $\overline{A} \cdot \overline{B} \cdot C$  não pode ser considerado um. Para a tabela verdade 2.2, só há a função canônica  $f(A, B, C) = A \cdot B \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot \overline{C}$  que a representa.

Tabela 2.2: Tabela verdade com mini-termos da função canônica  $f(A, B, C) = A \cdot B \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot \overline{C}$

| A | B | C | f(A, B, C) | Mini-termo                                           |

|---|---|---|------------|------------------------------------------------------|

| 0 | 0 | 0 | 1          | $\overline{A} \cdot \overline{B} \cdot \overline{C}$ |

| 0 | 0 | 1 | 0          |                                                      |

| 0 | 1 | 0 | 0          |                                                      |

| 0 | 1 | 1 | 0          |                                                      |

| 1 | 0 | 0 | 0          |                                                      |

| 1 | 0 | 1 | 0          |                                                      |

| 1 | 1 | 0 | 1          | $A \cdot B \cdot \overline{C}$                       |

| 1 | 1 | 1 | 0          |                                                      |

#### 2.1.6 Minimizando Funções Booleanas

Muitas vezes, quando se projeta um circuito combinacional, é desejável obter sua função mínima, ou seja aquela cujo número de operações é o menor possível, para que seja utilizado apenas o necessário, economizando recursos. Para isto existem técnicas de minimização como *Mapas de Karnaugh*, *Método de Quine-McCluskey*, dentre outros (Gudise and Venayagamoorthy [2003]).

Para otimizações de implementação, outras técnicas têm surgido, principalmente envolvendo conceitos de programação genética que serão discutidas mais adiante neste trabalho. Esta seção se limita somente à minimização lógica.

#### Mapas de Karnaugh

Mapas de Karnaugh são uma maneira de representar uma tabela verdade de tal modo que ela exponha características redundantes de um circuito. Eles se utilizam da forma canônica para suas construções. Suas células são compostas de valores 0 ou 1, sendo cada 1 um mini-termo desejado da função. Como exemplo, a função  $f(A,B,C) = \overline{A} \cdot B \cdot C + \overline{A} \cdot \overline{B} \cdot C + A \cdot \overline{B} \cdot C$  tem uma tabela verdade como mostra a tabela 2.3 e sua representação em mapa de Karnaugh se dá como mostra a tabela 2.4.

Tabela 2.3: Tabela verdade com mini-termos da função  $f(A,B,C)=\overline{A}\cdot B\cdot C+\overline{A}\cdot \overline{B}\cdot C+A\cdot \overline{B}\cdot C$

|   | A | B | C | f(A, B, C) | Mini-termo                                |

|---|---|---|---|------------|-------------------------------------------|

| ſ | 0 | 0 | 0 | 0          |                                           |

|   | 0 | 0 | 1 | 1          | $\overline{A} \cdot \overline{B} \cdot C$ |

|   | 0 | 1 | 0 | 0          |                                           |

|   | 0 | 1 | 1 | 1          | $\overline{A} \cdot B \cdot C$            |

|   | 1 | 0 | 0 | 0          |                                           |

|   | 1 | 0 | 1 | 1          | $A \cdot \overline{B} \cdot C$            |

| İ | 1 | 1 | 0 | 0          |                                           |

| l | 1 | 1 | 1 | 0          |                                           |

Tabela 2.4: Mapa de Karnaugh de  $f(A,B,C) = \overline{A} \cdot B \cdot C + \overline{A} \cdot \overline{B} \cdot C + A \cdot \overline{B} \cdot C$

$$f(A, B, C) : \begin{array}{c|c} & A \\ \hline C \\ \hline & 0 & 1 & 1 & 0 \\ \hline & 0 & 1 & 5 & 4 \\ \hline & 0 & 1 & 7 & 6 & 0 \\ \hline \end{array}$$

A tabela 2.5 exibe células que podem ser otimizadas da tabela 2.4. Isso ocorre pois o mapa de Karnaugh foi projetado para que células adjacentes difiram somente em um valor da entrada. Dessa forma, é possível retirar termos desnecessários da expressão lógica, se utilizando do fato que  $A + \overline{A} = 1$  e  $B + \overline{B} = 1$ .

Uma das otimizações marcadas na tabela 2.5 que pode ser feita é sobre os termos  $\overline{A} \cdot B \cdot C$  e  $\overline{A} \cdot \overline{B} \cdot C$ . Em ambos, a única variável que se altera é B. Por causa disso, é possível juntá-los, resultando no termo  $\overline{A} \cdot C$ . O mesmo ocorre para  $\overline{A} \cdot \overline{B} \cdot C$  e  $A \cdot \overline{B} \cdot C$ , ao retirar a variável A de ambos, o resultado é  $\overline{B} \cdot C$ .

No final, após todas as otimizações terem sido feitas, somam-se todos os termos gerados. No exemplo da tabela 2.5, seu circuito mínimo é  $\overline{A} \cdot C + \overline{B} \cdot C$ .

Tabela 2.5: Mapa de Karnaugh exibindo células passíveis de otimização.

A principal desvantagem de se usar mapas de *Karnaugh* é que o algoritmo funciona bem para até 6 variáveis de entrada, tornando-se impraticável para valores maiores. O número excessivo de células dificulta uma seleção razoável de saídas adjacentes (Mano [2006]).

#### Método de Quine-McCluskey

Uma função booleana também pode ser expressa de uma forma numérica. Cada minitermo é representado por um número, sendo ele a conversão binária de seus dígitos para decimal. Por exemplo, o minitermo de quatro variáveis  $\overline{A} \cdot B \cdot C \cdot D$  é expressado como 0111 em base binária, resultando no número 7 na base decimal.

Uma função booleana, portanto, também pode ser expressa como um somatório de mini-termos em sua representação decimal. Usando como exemplo a função da tabela 2.3, temos que ela pode ser expressa como  $\sum m_1 + m_3 + m_5$ , também sendo representada como  $\sum m(1,3,5)$ .

O método de *Quine-McCluskey*, também conhecido como método dos implicantes primos, visa amenizar a dificuldade vista para o método de *Karnaugh* para otimização de

funções com mais de seis variáveis. Ele consiste de duas partes: a primeira é achar todos os termos implicantes primos, ou seja, aqueles que são candidatos para inclusão no resultado final simplificado. A segunda é escolher, dentre esse termos, os que dão a expressão com o menor número de implicantes primários (Mano [2006]).

Para determinar quais termos são primos implicantes, cada mini-termo é comparado com todos os outros. Se eles diferem em apenas uma variável, ela é removida e um novo termo é formado. Isso se repete até que não seja mais possível combinar mais termos.

A tabela 2.6 demonstra isso para a função da tabela 2.3.

Tabela 2.6: Tabela de implicantes primos para a função  $\sum m(1,3,5)$ .

|              | -          |         | <u> </u>               |

|--------------|------------|---------|------------------------|

| Número de 1s | Mini-termo | Binário | Implicante (Tamanho 2) |

| 1            | $m_1$      | 001     | m(1,3)0-1              |

| 1            |            |         | m(1,5) - 01            |

| 9            | $m_3$      | 011     |                        |

| 2            | $m_5$      | 101     |                        |

O passo seguinte monta o gráfico dos implicantes primos, como pode ser visto na tabela 2.7.

Tabela 2.7: Gráfico de implicantes primos para a função  $\sum m(1,3,5)$ . Construído após o primeiro passo do algoritmo de Quine-McCluskey.

|        | 1 | 3 | 5 | Implicante | Expressão              |

|--------|---|---|---|------------|------------------------|

| m(1,3) | X | X |   | 0 - 1      | $\overline{A} \cdot C$ |

| m(1,5) | X |   | X | -01        | $\overline{B} \cdot C$ |

Ao final, todos os termos encontrados são somados. Para este exemplo, como visto na tabela 2.7, o resultado é  $\overline{A} \cdot C + \overline{B} \cdot C$ , chegando então na mesma expressão encontrada pelo método de Karnaugh.

### 2.2 Lógica Sequencial

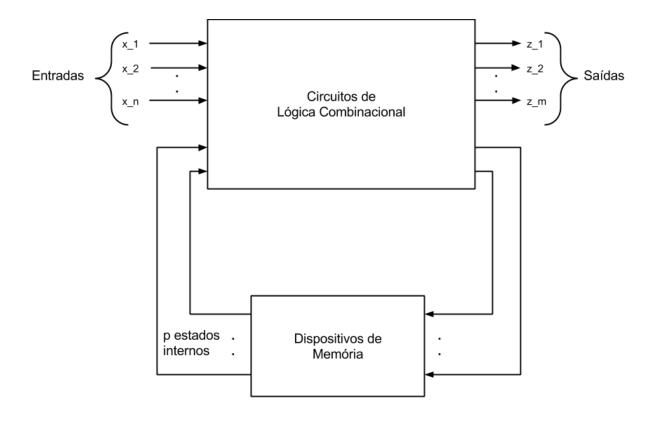

Até agora, a saída dos circuitos vistos na seção anterior dependiam apenas de suas entradas. Circuitos sequenciais utilizam-se tanto de circuitos combinacionais quanto de circuitos de retroalimentação. Isso possibilita a aplicação de uma abstração chamada estado. Dessa forma, torna-se muito comum a utilização e produção de chamadas máquinas de estado. A figura 2.9 mostra esse tipo de abordagem.

Um exemplo comum de circuito sequencial é o contador. Um contador é utilizado para a numeração de tíquetes de uma fila bancária, por exemplo.

#### 2.2.1 Elementos Básicos

Para que circuitos consigam manter estados, uma estrutura básica denominada flip-flop é utilizada. Nesta seção, será mencionado apenas o flip-flop tipo D, porém outros tipo podem ser encontrados.

Figura 2.9: Estrutura conceitual de uma máquina de estados.

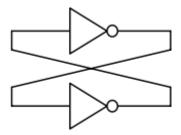

O *flip-flop* é um elemento capaz de guardar o valor de 1 *bit* (Tarnoff [2007]). Um pequeno circuito retroalimentado pode ser usado para alcançar este objetivo, apresentado na figura 2.10.

Figura 2.10: Estrutura realimentada estável independente de entradas (Tarnoff [2007]).

É possível ver que as saídas de ambas as portas está estável, tornando-as ideais para guardarem valores. A desvantagem desse circuito é a impossibilidade de alteração do valor armazenado, já que é completamente auto-contido.

A porta NAND, apresentada na seção 2.1.4, atua como um simples inversor se uma de suas saídas for mantida em 1. Dessa maneira, é possível replicar a estrutura da figura 2.10 utilizando portas NAND como mostra a figura 2.11.

Figura 2.11: Estrutura de retroalimentação utilizando portas NAND (Tarnoff [2007]).

Alterando os valores de uma das entradas, é possível alterar a saída das portas lógicas, com o circuito se estabilizando novamente no momento em que as duas entradas retornarem para 1.

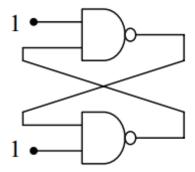

Caso a entrada superior receba o rótulo S e a inferior R, correspondente às saídas Q e  $\overline{Q}$ , o elemento é chamado de *latch* RS, e é utilizado na maior parte de circuitos que necessitam armazenar dados. Seu diagrama pode ser visto na figura 2.12.

Figura 2.12: Diagrama de um latch RS (Wikipedia [2014b]).

#### Latch D

Um possível módulo que pode ser formado pelo  $latch\ RS$  é o latch tipo D, que tem a interface definida na figura 2.13, onde a saída Q é o valor armazenado no circuito, E é o valor que determina se o valor D é armazenado no latch.

A entrada E funciona como uma porta. Se estiver no nível 1 (aberta), qualquer alteração no valor D causa uma alteração na saída do circuito. Se estiver em 0 (fechada), o valor da saída se mantém estável mesmo que o valor D se altere. Seu comportamento completo pode ser visto na tabela verdade 2.8.

#### Flip-flop D

Latches são normalmente categorizadas como sensíveis a nível, ou seja, se seu nível de enable estiver em alto, todas as alterações de D são vísiveis na saída do latch. Flip-flops, diferentemente, só causam alterações na saída nas transições  $0 \to 1$  ou  $1 \to 0$  do enable, também chamado de clock no caso de flip-flops. A essas duas categorias dão-se os nomes de positive edge triggered e negative edge triggered (Tarnoff [2007]).

Figura 2.13: Diagrama de um latch D (Wikipedia [2014b]).

Tabela 2.8: Tabela verdade da estrutura latch D.

| En | tradas | Saídas |                |  |

|----|--------|--------|----------------|--|

| E  | D      | Q      | $\overline{Q}$ |  |

| 0  | X      | Q      | $\overline{Q}$ |  |

| 1  | 0      | 0      | 1              |  |

| 1  | 1      | 1      | 0              |  |

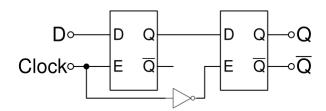

A estrutura interna de um flip-flop D de negative edge, ou seja, com mudança de saída apenas durante a transição  $1 \to 0$ , pode ser vista na figura 2.14.

Figura 2.14: Diagrama de um flip-flop D (Wikipedia [2014b]).

Este tipo de *flip-flop*, em especial, é chamado de *master-slave*. Com o circuito montado dessa maneira, sua tabela verdade pode ser vista na tabela 2.9.

Tabela 2.9: Tabela verdade do flip-flop tipo D.

| Entrac            | Saí | das |                |

|-------------------|-----|-----|----------------|

| Clock             | D   | Q   | $\overline{Q}$ |

| $1 \rightarrow 0$ | 0   | 0   | 1              |

| $1 \rightarrow 0$ | 1   | 1   | 0              |

| 0                 | X   | Q   | $\overline{Q}$ |

| 1                 | X   | Q   | $\overline{Q}$ |

#### 2.2.2 Máquina de Estados Finitos

A abstração e modelagem de problemas que se utilizam de circuitos sequenciais normalmente se dá por meio das chamadas máquinas de estados.

Uma máquina de estados pode ser definida como uma quíntupla  $M=(Y,X,Z,\alpha,\beta)$ . Y é o conjunto de todos os estados existentes na máquina. X é o conjunto de entradas para a máquina. Z, o conjunto de todos os estados de saída possíveis da máquina.  $\alpha$  é a função  $\alpha:(Y\times X)\to Y$ , que define o próximo estado com base no estado atual e entrada atual. A função  $\beta$  define a saída atual da máquina, sua definição formal depende da classificação da máquina como Moore ou Mealy (Belgasem [2003]).

#### Máquina de Moore

Para máquinas de Moore, a função  $\beta$  é definida como:

$$\beta: Y \to Z$$

ou seja, a saída atual do circuito depende apenas de seu estado atual.

#### Máquina de Mealy

No caso de máquinas de Mealy, a saída atual da máquina depende tanto do estado atual quanto da entrada atual. Ou seja, sua função  $\beta$  é da forma

$$\beta: (Y \times X) \to Z$$

.

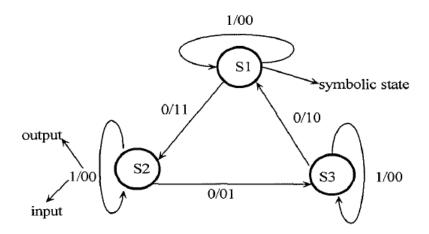

#### Comparação

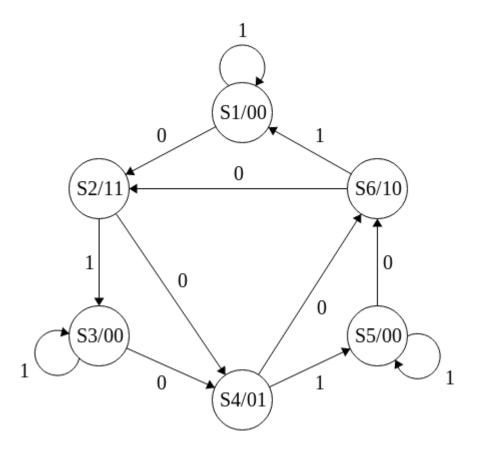

Máquinas de estados são frequentemente representadas utilizando grafos especiais chamados Diagramas de Transições e Estados (Belgasem [2003]). Um exemplo de uma máquina de Mealy com uma entrada e duas saídas pode ser visto na figura 2.15, onde cada nó representa um estado (com seu rótulo) e os números nas arestas indicam as entradas e as saídas associadas. Sua tabela de transições associada está descrita na tabela 2.10.

Figura 2.15: Exemplo de Diagrama de Transições e Estados (Belgasem [2003]).

Tabela 2.10: Exemplo de tabela de transição de estados.

| Entrada | Estado Atual | Próx. Estado | Saída |

|---------|--------------|--------------|-------|

| 0       | $S_1$        | $S_2$        | 11    |

| 0       | $S_2$        | $S_3$        | 01    |

| 0       | $S_3$        | $S_1$        | 10    |

| 1       | $S_1$        | $S_1$        | 00    |

| 1       | $S_2$        | $S_2$        | 00    |

| 1       | $S_3$        | $S_3$        | 00    |

A mesma máquina implementada utilizando o paradigma de Moore teria um diagrama de transições e estados como mostra a figura 2.16, com uma tabela de transições descrita na tabela 2.11.

Figura 2.16: Exemplo de Diagrama de Transições e Estados utilizando o paradigma de Moore.

Em geral, máquinas de Moore possuem uma saída mais simples de ser entendida, já que depende apenas de um fator. Além disso, são mais seguras pois se a entrada for assíncrona com o *clock* da máquina, então ocorrem condições de corrida. Em contrapartida, máquinas de Mealy são significativamente mais compactas, possuindo menos estados em geral.

Tabela 2.11: Tabela de transições de estados para o exemplo utilizando o paradigma de Moore.

| Estado Atual/Saída | Prox. Estado |       |

|--------------------|--------------|-------|

| Estado Atual/Salda | 0            | 1     |

| $S_1/00$           | $S_2$        | $S_1$ |

| $S_{2}/11$         | $S_4$        | $S_3$ |

| $S_3/00$           | $S_4$        | $S_3$ |

| $S_4/01$           | $S_4$ $S_6$  | $S_5$ |

| $S_5/00$           | $S_6$        | $S_5$ |

| $S_{6}/10$         | $S_2$        | $S_1$ |

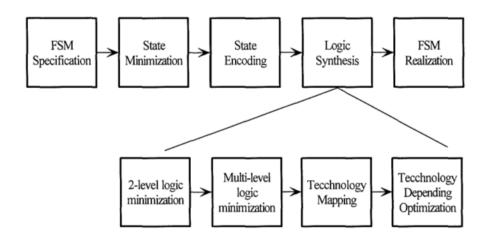

#### 2.2.3 Processo de *Design*

De acordo com Belgasem [2003], o processo de projeto de um circuito sequencial, assim como a abordagem tradicional para outros problemas, é dividir a especificação em subetapas. Cada uma deve ter, idealmente, pouca ou nenhuma relação com as outras. O objetivo é conseguir, a partir da especificação de um problema, desenvolver uma máquina de estados finitos que o resolva. Um esquema de como isso é normalmente feito está na figura 2.17.

Figura 2.17: Processo de projeto de um circuito sequencial (Belgasem [2003]).

A razão disso vem do fato de que o problema de sintetizar um circuito sequencial é um problema considerado difícil. Belgasem [2003] cita a grande quantidade de possíveis implementações possíveis para um dado problema, além de outros fatores como área que o circuito ocupa e seu gasto de energia para a determinação de uma boa solução.

#### Especificação da Máquina

Este passo consiste na configuração inicial desenvolvida pelos projetistas do circuito. Normalmente contém o diagrama de estados e transições com uma tabela de transições de estados.

#### Minimização de Estados

Muitas vezes, a máquina inicialmente gerada não possui um número ótimo de estados. Um método clássico para realizar isso é incorporar don't cares, ou seja, valores que em um dado instante não são importantes, na tabela de transições e, consequentemente, no diagrama de transições e estados.

Em contrapartida, outras abordagens de minimização focam não só no número de estados mas na complexidade lógica da minimização ótima, Avedillo et al. [1991] menciona que nem sempre é desejável se ter o número mínimo de estados.

#### Codificação de Estados

Em implementações de máquinas de estados, os estados são representados por *strings* de *bits*. O problema que estuda a relação de mapeamento entre estados e *strings* de *bits* que possui o menor custo é chamado de Problema da Codificação de Estados (Amaral et al. [1995]).

Para essa etapa, diversos autores já tentaram diferentes abordagens (Belgasem [2003]). Em geral, são utilizadas heurísticas para solucionar esse tipo de problema. Dentre elas, algoritmos genéticos foram usados com sucesso (Amaral et al. [1995]), porém o problema ainda é considerado difícil.

#### Síntese do Circuito

Atualmente, existe uma vasta gama de ferramentas dedicadas a síntese a partir de uma descrição da máquina. As formas mais comuns de se descrever circuitos sequenciais são pelas linguagens denominadas Hardware Description Language (HDL), como VHDL e Verilog (Belgasem [2003]).

As máquinas são simuladas e testadas em dispositivos específicos denominados reconfiguráveis. Com os objetivos alcançados, é feito um Application-Specific Integrated Circuit (ASIC) a partir da descrição resultante.

A seguinte seção trata de um dos tipos mais utilizados de dispositivos reconfiguráveis, extremamente útil para o desenvolvimento de circuitos não só sequenciais, mas de forma geral.

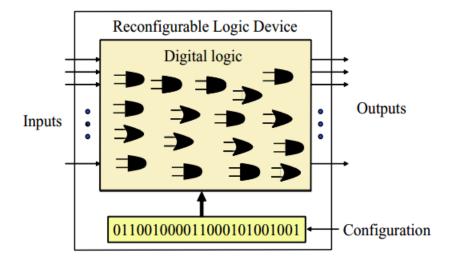

### 2.3 Dispositivo Reconfigurável - FPGA

Um Field-Programmable Gate Array (FPGA) é um dispositivo lógico que consiste de um arranjo bidimensional de chamadas células lógicas e chaves programáveis. Cada célula lógica pode ser programada para exercer uma função booleana, cujo valor é disponibilizado para células vizinhas através dessas chaves (Chu [2008]). Células especiais, principalmente as que estão na borda do arranjo, se conectam a portas destinadas a canais de I/O.

Em um dado momento, a configuração da FPGA é determinada por uma memória on-chip, que pode ser modificada por software. Apesar da configuração do circuito não se modificar, as mudanças realizadas a essa memória fazem com que as ligações entre células lógicas e suas configurações se modifiquem, portanto, exercendo a função de um novo circuito (Thompson [1998]), como mostra a figura 2.18.

Figura 2.18: Configuração de memória mapeando para um circuito em um dispositivo reconfigurável (Torresen [2004]).

Cada célula lógica tipicamente consiste de uma Look-up Table (LUT) configurável de 3 ou 4 entradas, ou seja uma tabela verdade que descreve uma função booleana, e um flip-flop tipo-D. Por exemplo, a célula da família de FPGAs Cyclone II pode ser vista na figura 2.19.

Figura 2.19: Logic Element (LE) da família de FPGAs Cyclone II (Altera [2007]).

FPGAs pertencem a uma classe de dispositivos chamada Field-Programmable Logic (FPL) (Meyer-Baese [2007]), pois o processo de programação pode ser feito várias vezes após a produção do dispositivo.

A figura 2.20 mostra conceitualmente como o arranjo de células é feito.

Existe uma variedade grande de diferentes tipos de dispositivos reconfiguráveis. Para este trabalho, o foco será apenas em FPGAs por suas facilidades de reconfiguração apresentadas.

Figura 2.20: Arranjo conceitual de elementos lógicos e chaves programáveis (Chu [2008]).

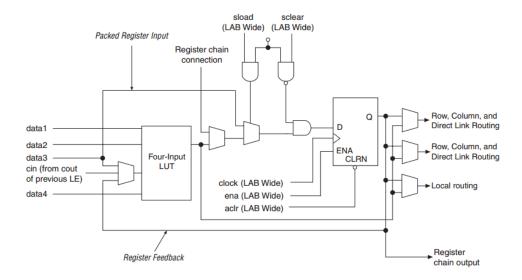

### 2.3.1 FPGA Altera Cyclone IV EP4CE115

Esta seção detalhará brevemente a FPGA Altera Cyclone IV EP4CE115 que será utilizada para este trabalho. Consiste de 114,480 elementos lógicos básicos cujas estruturas podem ser vistas na figura 2.21. É possível observar que o elemento lógico básico constitui de LUTs de 4 entradas, blocos de memória e multiplicadores (Altera [2013]).

Cada elemento lógico está contido em um conjunto denominado Logic Array Block (LAB). A troca de informações dentro de um mesmo LAB ocorre por um barramento local, como mostra a figura 2.22. Esse barramento também é usado para trocar informações com estruturas adjacentes.

Além disso, outras características relevantes ao *chip* são:

- 3888 Kbits de memória embarcada;

- 266 Multiplicadores 18 × 18 bits;

- 4 circuitos PLL de livre uso;

- 528 pinos de I/O para usuário.

A FPGA está integrada à placa de desenvolvimento *Altera DE2-115*, cujo *layout* pode ser visto na figura 2.23.

O *chip* principal apresenta diversas interfaces para dispositivos externos. Dentre outros é possível listar (Altera [2010]), para memórias:

• 128MB (32Mx32*bit*) SDRAM;

Figura 2.21: LE da família de FPGAs Cyclone IV (Altera [2013]).

Figura 2.22: LAB com barramento de interconexão local (Altera [2013]).

- 2MB (1Mx16) **SRAM**;

- 8MB (4Mx16) Flash com modo 8-bits;

- 32KB EEPROM.

Figura 2.23: Layout da placa de desenvolvimento Altera DE2-115 (Altera [2010]).

Três *clocks* de 50MHz, conectores USB tipos A e B, uma porta de expansão de 40 pinos.

Para interface direta com o usuário,

- 18 chaves deslizantes e 4 de botão;

- 18 LEDs vermelhos e 9 verdes;

- 8 displays de 7 segmentos.

Todos esses recursos tornam a placa de desenvolvimento e a FPGA ferramentas convenientes para projetar circuitos. Com a capacidade de gerar qualquer sistema computacional e ser reconfigurável torna este ambiente ideal para rápidas iterações de configurações, tarefa necessária para que este estudo seja viável.

#### Processo de Design

Empresas fabricantes de FPGAs tipicamente oferecem softwares que facilitam o desenvolvimento em suas plataformas. Em geral, esses programas têm a responsabilidade de auxiliar a etapa de compilação (exemplo na figura 2.24) da descrição de um circuito para o bitstream de configuração específico de alguma FPGA, passando pelas fases de análise, síntese e montagem do projeto. Para os chips do fabricante Altera, esse software de desenvolvimento se chama Quartus II.

Após a compilação do circuito, esses programas costumam oferecer também mecanismos de *download* das descrições geradas para o *chip*, configurando-o com a funcionalidade desejada.

|     | Task                                   | <b>O</b> Time |

|-----|----------------------------------------|---------------|

| 75% |                                        | 00:00:19      |

| ✓   |                                        | 00:00:05      |

| ✓   |                                        | 00:00:09      |

| ✓   | Assembler (Generate programming files) | 00:00:05      |

| 0%  |                                        | 00:00:00      |

|     |                                        |               |

|     | Program Device (Open Programmer)       |               |

Figura 2.24: Etapas típicas de compilação para bitstream alvo.

# 2.4 Algoritmos Genéticos

De acordo com o trabalho de Darwin [1859], as características das espécies são determinadas não por intervenções divinas como se acreditava na época anterior à publicação desse trabalho, mas sim por um mecanismo denominado seleção natural.

Darwin [1859] argumenta que indivíduos mais adaptados de uma população têm maiores chances de se reproduzirem. Como consequência disso, seus genes têm uma probabilidade maior de serem passados para as gerações seguintes. Devido a isso, a cada nova geração, os genes da população tendem a se convergir para aquele que está mais adaptado ao ambiente.

Pode se ver que, aplicado em escalas de milhões de anos, esse mecanismo de seleção natural exibe características bastante interessantes nas espécies. Há muito se busca uma maneira de imitar esse tipo de comportamento e aplicá-lo a outros tipos de problemas, dando origem à área de Algoritmos Genéticos.

Conceito inventado por John Holland na década de 60 (Melanie [1999]), seu objetivo era estudar o fenômeno de adaptação que ocorre na natureza visando desenvolver mecanismos similares para sistemas computacionais.

Antes de aplicar uma abordagem genética a um problema, é preciso torná-lo apto a isso. Um dos primeiros requisitos é conseguir descrevê-lo com base em todos os parâmetros necessários, ou seja, suas possíveis soluções. Estas são denominadas os indivíduos da população. Cada indivíduo é representado por um cromossomo, ou seja, um conjunto de genes, que formam os parâmetros mencionados. Por sua vez, genes são representados por um conjunto de "alelos" possíveis, que no contexto computacional pode ser descrito como os dois valores válidos para um bit: 0 e 1. Dessa forma é possível resumir um indivíduo em uma lista de 0s e 1s.

# 2.4.1 Operadores Genéticos

Nesta seção, serão introduzidos operações comumente utilizadas em algoritmos genéticos.

#### Reprodução ou Crossover

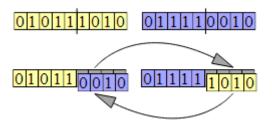

Esta operação busca imitar o fenômeno da recombinação genética. Um ponto de separação do cromossomo é escolhido aleatoriamente e dois novos indivíduos são gerados a partir da permuta da informação genética entre os dois cromossomos selecionados. A figura 2.25 ilustra essa operação.

Figura 2.25: Exemplo de crossover entre dois cromossomos (Wikipedia [2014a]).

#### Mutação

A mutação visa simular a situação em que o cromossomo é alterado por erros durante a divisão celular. Essas mudanças são essenciais para o surgimento de novas características.

No caso de algoritmos genéticos, essa mudança se representa por uma probabilidade  $p_m$ . Em geral, a mutação atua na construção de novos indivíduos. Ou seja, em sua criação, há uma probabilidade de  $p_m$  de haver uma mutação. Mutações costumam alterar um ou mais alelos aleatórios como mostra a tabela 2.12.

Tabela 2.12: Exemplo de operação de mutação em um cromossomo.

| Cromossomo Inicial | 0110010111001011                |

|--------------------|---------------------------------|

| Cromossomo Mutante | 01100101110 <mark>1</mark> 1011 |

#### Função de fitness

As funções de *fitness* têm como entrada um cromossomo e saída um valor de avaliação, dependendo do quão perto ele chega da solução, ou seja, atuam definindo aqueles que estão mais ou menos aptos a ter seus genes passados adiante. A função de *fitness* é considerada um dos pontos mais sensíveis de um algoritmo genético.

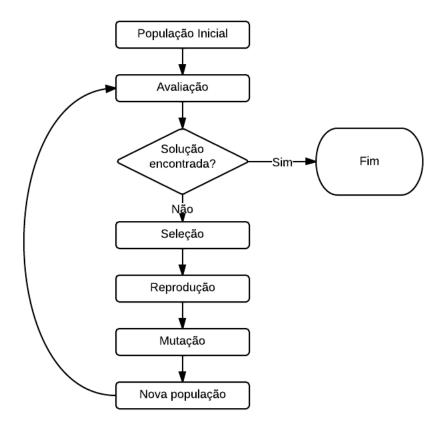

Uma vez definidos os operadores básicos, um algoritmo genético pode ser definido na série de passos apresentada na figura 2.26.

# 2.4.2 Operação de Seleção

Essa operação consiste em selecionar cromossomos mais adaptados para a reprodução. Quanto mais adaptado, maior é sua chance de ser escolhido, mas não há garantia de que isso ocorra. Dentre os diversos métodos de seleção, os mais populares são as estratégias de seleção por roleta ou por torneio descritos a seguir.

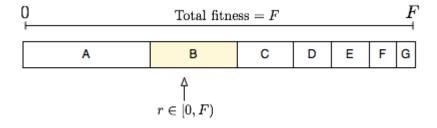

#### Seleção por Roleta

A seleção por roleta se assemelha bastante a uma roleta real de cassino, de onde seu nome é derivado. Em geral, nela, indivíduos que possuem fitness maiores possuem uma maior probabilidade de serem escolhidos, porém não se garante a escolha. A probabilidade é distribuída relativamente para cada indivíduo, ou seja, a soma de todas as probabilidades deve ser 1, e deve ser proporcional ao fitness de cada um.

Figura 2.26: Passos gerais para um algoritmo genético.

Dessa maneira, a forma de se calcular o *fitness relativo* do n-ésimo indivíduo é dada por

$$f_r(x_n) = \begin{cases} \frac{f(x_n)}{\sum_{i=1}^N f(x_i)}, & \text{se } n = 1\\ f_r(x_{n-1}) + \frac{f(x_n)}{\sum_{i=1}^N f(x_i)}, & \text{senão} \end{cases}$$

(2.1)

onde N é o tamanho da população.

Após o cálculo dos *fitness* relativos, gera-se um número aleatório  $0 \le r < 1$ , escolhendo aquele indivíduo em que r pertence ao intervalo entre um *fitness* relativo e outro. Uma representação visual deste processo pode ser visto na figura 2.27.

Figura 2.27: Exemplo da seleção por roleta (Wikipedia [2014c]).

Na figura 2.27, o individuo A possui o maior *fitness*, tendo portanto uma maior probabilidade de ser selecionado. Por outro lado, o indivíduo G é o menos adaptado, possuindo a menor probabilidade de seleção.

#### Seleção por Torneio

A seleção por torneio busca simular o fato de que uma população inteira, salvo poucas exceções, nunca está competindo contra si como um todo, mas sim por pequenas competições localizadas.

Miller et al. [1995] cita que algumas vantanges de implementações desse tipo de seleção são: a facilidade de escrita, eficiência do ponto de vista de paralelismo e providenciam um maior controle sobre a pressão da seleção. Essa pressão é definida como o grau em que indivíduos mais adaptados são favorecidos. Trabalhos anteriores como o de Miller et al. [1995] também citam que o sucesso de um algoritmo genético depende, em maior parte, da pressão da seleção. Se a pressão for muito baixa, a taxa de convergência será desnecessariamente baixa. Se for muito alta, é grande a chance de que a convergência ocorra em uma solução não-ideal.

Dada uma população P, e um tamanho de torneio k, a seleção por torneio seleciona um conjunto aleatório de k indivíduos de P para competirem entre si, e, para cada torneio, escolhendo aquele mais adaptado. Seu pseudo-código correspondente pode ser visto no algoritmo 1.

```

\begin{split} \textbf{Input:} \ P, \ k \\ \textbf{Result:} \ & \textbf{Individuo mais adaptado} \\ \textit{melhor.} \textit{fitness} \leftarrow 0; \\ \textbf{for} \ 1 \ to \ k \ \textbf{do} \\ & | \ \textit{competidor} \leftarrow P[random()]; \\ & | \ \textbf{if} \ \textit{competidor.} \textit{fitness} > \textit{melhor.} \textit{fitness} \ \textbf{then} \\ & | \ \textit{melhor} \leftarrow \textit{competidor}; \\ & | \ \textbf{end} \\ \textbf{end} \\ \textbf{return} \ \textit{melhor} \\ & \quad \textbf{Algoritmo} \ \textbf{1:} \ \textbf{Algoritmo} \ \textit{para seleção} \ \textit{de um individuo por torneio.} \end{split}

```

A escolha do melhor indivíduo de uma população é realizada pela simples escolha do indivíduo com maior fitness em torneio de tamanho k.

Apesar do tamanho ideal do torneio variar de acordo com o problema (Xie and Zhang [2009]), normalmente são escolhidos valores não muito altos para k. De fato, muitas vezes k=2 é o valor utilizado, chamado de torneio binário. Observe que para k=1, a seleção por torneio se reduz a uma seleção aleatória.

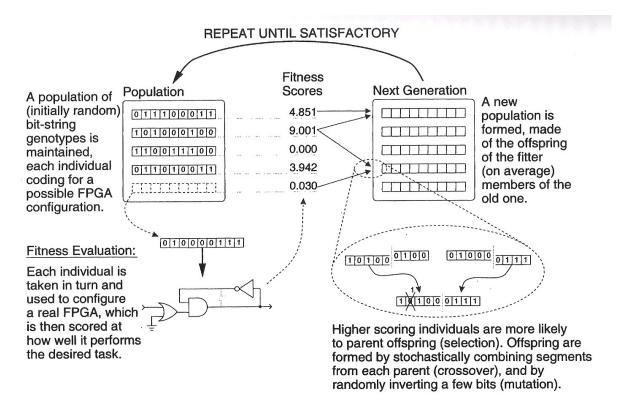

# 2.5 Programação Genética Cartesiana

A Programação Genética Cartesiana (Cartesian Genetic Programming (CGP)), tem como característica principal a linearização de um cromossomo para representar uma rede, utilizando-se números inteiros. O termo *cartesiano* vem do fato do método consistir em uma grade bidimensional de nós (Miller [1999]).

O cromossomo é dividido em duas seções distintas: nós e saídas. Cada gene da seção de nós identifica dois componentes básicos de um nó:

- 1. A operação realizada pelo nó;

- 2. As entradas usadas para o cálculo.

A seção de saídas indica a que nó cada saída deve se ligar para produzir seu resultado. A descrição que o cromossomo representa é conhecida como *genótipo*. O programa resultante da decodificação desse genótipo é chamado de fenótipo. Para CGP, enquanto o genótipo possui tamanho fixo, descrevendo completamente a grade, o fenótipo efetivo varia com o número de nós utilizados desde zero até todos os disponíveis no genótipo (Miller [2011]).

#### 2.5.1 Forma Geral

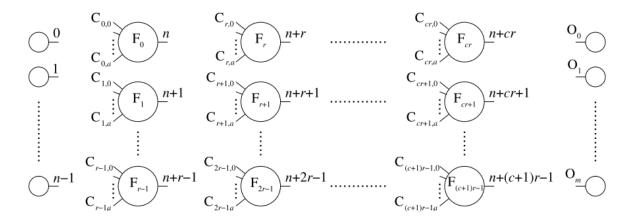

Se  $n_i$  é o número de entradas necessárias para o programa e  $n_o$  o número de saídas, um sistema genético cartesiano de  $N=n_r\times n_c$  nós, cada qual com r entradas, tem seu endereçamento de cromossomos da seguinte maneira:

$$F_0C_{0,0}\cdots C_{0,r-1}F_1C_{1,0}\cdots C_{1,r-1}\cdots F_{N-1}C_{n_c*n_r,0}\cdots C_{n_c*n_r,r-1}O_0\cdots O_{n_o-1}$$

onde  $n_r$  indica o número de linhas,  $n_c$  o número de colunas,  $F_k$  é a função que o nó de número k exerce, C é o endereço de onde provém o valor de entrada e os valores  $O_l$  indicam de qual nó a saída l retira seu valor.

Um parâmetro adicional l indica o número de colunas anteriores que a coluna j pode usar para valores de entradas de seus nós, limitando sua escolha de colunas para  $[max(0,j-l),\cdots,(j-1)]$ . Dessa forma, não são permitidas retroalimentações, gerando uma topologia com apenas ligações feedforward. Uma visualização gráfica da forma geral pode ser vista na figura 2.28.

Figura 2.28: Forma geral da estrutura de um sistema genético cartesiano (Miller [2011]).

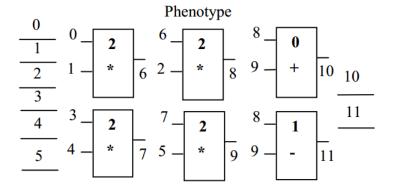

O exemplo da figura 2.29 mostra um sistema com  $n_i = 6$ ,  $n_o = 2$ ,  $n_r = 2$ ,  $n_c = 3$ , r = 2 e l = 2. É possível observar a tradução que ocorre entre a descrição do genótipo para o fenótipo. No fenótipo, é instanciado um grafo de elementos lógicos, com suas ligações e

funções definidas pelo genótipo. As saídas do circuito constituem os dois últimos elementos do genótipo.

Figura 2.29: Exemplo de sistema cartesiano genético. Evidencia relação entre genótipo e fenótipo (Miller [1999]).

## 2.5.2 Restrição de Valores

Para a variável F, que indica a função do nó, seja  $n_f$  o número de funções possíveis do sistema, então

$$0 \le F < n_f$$

.

Para as entradas do nó  $C_{i,j}$ , deve se respeitar o valor l de níveis atingíveis. Portanto,

$$n_i + (j-l)n_r \le C_{i,j} \le n_i + jn_r$$

para  $j \geq l$  e

$$0 \le C_{i,j} \le n_i + jn_r$$

para j < l. Para os valores de saída O, segue-se a seguinte restrição:

$$0 \leq O < n_i + N$$

.

Tipicamente, conforme apresentado na seção 2.5.1, sistemas genéticos cartesianos não possuem ciclos. Para que o objetivo de liberação de restrições seja melhor atendido, não será usada a variável l que indica o número de colunas anteriores atingíveis. Para este trabalho colunas poderão usar quaisquer outras como possíveis valores. Dessa forma, torna-se possível a retroalimentação, estrutura imprescindível em circuitos capazes de armazenar dados, tais como latches e flip-flops.

### 2.5.3 Estratégia evolucionária $(1 + \lambda)$

Primeiramente definido por Beyer [1993] o algoritmo  $(1+\lambda)$  para geração e seleção de uma nova população vem sendo utilizado pela comunidade científica (Hilder et al. [2010], Walker et al. [2009]) como escolha de estratégia evolutiva em problemas CGP. Miller et al. [2000] o descreve como uma estratégia eficiente e de implementação simples. Seu nome vem do fato de haver somente 1 indivíduo, gerando  $\lambda$  outros indivíduos por mutações. Seu algoritmo está descrito no algoritmo 2.

```

Input: B, cromossomo com maior fitness.

Result: Melhor indivíduo encontrado.

C \leftarrow \lambda mutações de B;

M = \{c | c \in C, c. fitness \geq B. fitness\};

if M \neq \emptyset then

\mid B \leftarrow max(M);

end

return B

Algoritmo 2: Algoritmo que descreve a estratégia (1 + \lambda).

```

Uma visualização gráfica pode ser vista na figura 2.30, onde  $\lambda=4$ . Nela, o indivíduo 1, que gera suas  $\lambda$  mutações, está sempre no topo da gerações. Na geração 0, como nenhum indivíduo gerado a partir do 1 possui um *fitness* igual ou maior a ele, ele é passado como o 1 da seguinte geração. Na geração 1, um dos indivíduos gerados possui um *fitness* igual a seu gerador, tornando-o indivíduo 1 da geração 2. Esse processo se repete até que o objetivo desejado seja alcançado.

Figura 2.30: Exemplo de execução do algoritmo  $(1 + \lambda)$ .

A principal diferença entre esse algoritmo e os descritos anteriormente é que seu operador principal é a mutação, não havendo operações de *crossovers*. Todos os  $\lambda$  indivíduos são gerados a partir de mutações do individuo pai. De acordo com Miller et al. [2000], tipicamente  $\lambda = 4$ .

O algoritmo  $(1 + \lambda)$  é naturalmente elitista. O indivíduo com maior *fitness* sempre é preservado para gerações seguintes.

#### 2.5.4 Neutralidade

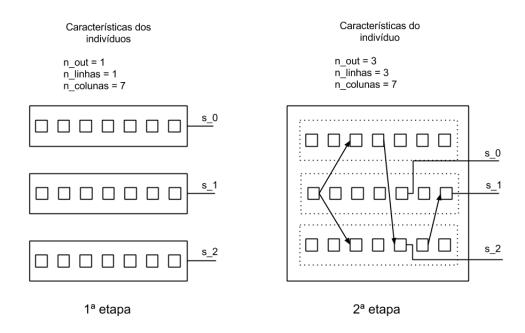

CGP representa o genótipo como uma lista de tamanho fixo de números inteiros que indicam as propriedades de cada nó em um grafo. O fenótipo resultante, porém, é resultado da aplicação das ligações desses nós no genótipo. Portanto, o fenótipo possui um tamanho variável, havendo então genes inativos, ou seja, que não possuem efeito algum na avaliação de seu *fitness*. À existência de genes inativos dá-se o nome de *neutralidade*.