### TRABALHO DE GRADUAÇÃO

# Projeto de um Sintetizador de Frequência em 920MHz para um Receptor CMOS Embarcado em um SoC

**Leonardo Camargo Neves**

Brasília, agosto de 2010

### **UNIVERSIDADE DE BRASILIA**

**FACULDADE DE TECNOLOGIA**

# UNIVERSIDADE DE BRASILIA Faculdade de Tecnologia

### TRABALHO DE GRADUAÇÃO

### Projeto de um Sintetizador de Frequência para Transceptor CMOS 920MHz Embarcado em um SoC

#### **Leonardo Camargo Neves**

Relatório submetido como requisito parcial para obtenção do grau de Engenheiro Eletricista

#### **Banca Examinadora**

| Prof. José Camargo da Costa, UnB/ Dep        |  |

|----------------------------------------------|--|

| (Orientador)                                 |  |

| Prof. Ricardo Zelenovsky, UnB/ Dep           |  |

| (Examinador Interno)                         |  |

| Heider Marconi Guedes Madureira, UnB/ Mestre |  |

| (Examinador Interno)                         |  |

#### Dedicatória

Dedico este trabalho a minha família, parentes, amigos, colegas...enfim, a todos aqueles que me ajudaram a chegar até este ponto

Leonardo Camargo Neves

#### **RESUMO**

Este trabalho apresenta o projeto de um sintetizador de frequência em tecnologia 0.35μm 3.3V CMOS, baseado na arquitetura de um *Phase-Locked Loop* (PLL) capaz de sintetizar a frequência de 920MHz - faixa de 890MHz a 1050MHz - utilizando uma topologia de VCO com compensação de atraso.

São apresentadas as etapas de desenvolvimento de cada um dos circuitos que fazem parte do PLL, bem como os problemas e limitações encontrados em cada um dos projetos.

# SUMÁRIO

| 1 INTRODUÇÃO                                           |    |

|--------------------------------------------------------|----|

| 1.1 DEFINIÇÃO DO PROBLEMA                              |    |

| 1.2 ORGANIZAÇÃO DO TRABALHO                            |    |

| 2 REVISÃO BIBLIOGRÁFICA                                | 2  |

| 2.1 O RECEPTOR                                         |    |

| 2.2 PHASE-LOCKED LOOP DEFINIÇÃO E COMPONENTES          | 2  |

| 2.2.1 VOLTAGE CONTROLLED OSCILLATOR (VCO)              | 3  |

| 2.2.2 LOOP FILTER (LF)                                 |    |

| 2.2.3 CHARGE PUMP (CP)                                 |    |

| 2.2.4 PHASE FREQUENCY DETECTOR (PFD)                   |    |

| 2.2.5 DIVISOR DE FREQUÊNCIA                            |    |

| 2.3 ESTUDO DO PLL NO DOMÍNIO s                         | 5  |

| 3 METODOLOGIA                                          | 8  |

| 3.1 O PLL                                              | 8  |

| 3.2 O VCO                                              |    |

| 3.3 O LF                                               | 9  |

| 3.4 O CHARGE PUMP                                      |    |

| 3.5 O PFD                                              | 11 |

|                                                        |    |

| 4 PROJETO                                              |    |

| 4.1 PROJETO DO VCO                                     | 12 |

| 4.2 PROJETO DO LOOP FILTER                             | 12 |

| 4.3 PROJETO DO CHARGE PUMP                             | 12 |

| 4.4 PROJETO DO PFD                                     |    |

|                                                        |    |

| 5 RESULTADOS                                           |    |

| 5.1 VCO                                                |    |

| 5.2 LOOP FILTER                                        |    |

| 5.3 CHARGE PUMP                                        |    |

| 5.5 PLL COMPLETO                                       |    |

|                                                        |    |

| 6 CONCLUSÕES                                           | 24 |

| 7 REFERÊNCIAS BIBLIOGRÁFICAS                           | 25 |

| 8 ANEXOS                                               | 97 |

| 8.1 SIMULAÇÃO TRANSIENTE                               | ۵7 |

| 8.2 SIMULAÇAO TRANSIENTE                               | 27 |

| 8.3 SIMULACAO POSE                                     |    |

| 8 4 POTINA PAPA CÁLCULO DOS PAPÂMETROS DO LE NO MATLAR | 30 |

# LISTA DE FIGURAS

| Figura | 2.1 - | Diagrama de Blocos do Receptor                                                          | . 2 |

|--------|-------|-----------------------------------------------------------------------------------------|-----|

|        |       | Diagrama de Blocos do PLL                                                               |     |

| Figura | 2.3 - | Circuito do Charge Pump com Loop Filter                                                 | . 4 |

| Figura | 2.4 - | Circuito do PFD                                                                         | . 5 |

| Figura | 2.5 - | Lugar Geométrico das Raízes para a função de transferência do loop                      | . 7 |

|        |       | Esquemático do VCO                                                                      |     |

|        |       | Esquemático do VCO com carga funcionando como controle                                  |     |

|        |       | Esquemático do Charge Pump                                                              |     |

| Figura | 5.1 - | Esquemático do VCO com duas saídas e cinco estágios                                     | 15  |

| Figura | 5.2 - | Esquemático do VCO com o transistor pmos funcionando como chave e um                    |     |

|        |       | INV3 e uma CLKINV15 em cada saída                                                       |     |

|        |       | Saídas do VCO. Pode-se observar a defasagem de 180° entre elas                          |     |

| Figura | 5.4 - | Leiaute do VCO com cinco estágios, Enable e uma INV3 e uma CLKINV15 e                   |     |

|        |       | cada saída                                                                              |     |

| Figura | 5.5 - | Curva característica do VCO com cinco estágios, Enable e uma INV3 e uma                 |     |

|        |       | CLKINV15 em cada saída                                                                  |     |

|        |       | Leiaute do LF                                                                           |     |

|        |       | Simulação transiente do LF                                                              |     |

|        |       | Esquemático do CP                                                                       |     |

|        |       | Leiaute do circuito do CP                                                               |     |

|        |       | – Simulação do CP                                                                       |     |

| _      |       | <ul> <li>Leiaute do Divisor (acima) juntamente com o leiaute do PFD (abaixo)</li> </ul> |     |

| _      |       | - Leiaute do PLL                                                                        |     |

|        |       | Caixa de diálogo da Simulação Transiente                                                |     |

|        |       | Caixa de diálogo da Simulação PSS                                                       |     |

| Figura | 8.3 – | Caixa de diálogo da Simulação PNOISE                                                    | 29  |

# LISTA DE TABELAS

| Tabela 5.1 – Dimensões dos componentes do VCO                                | 14 |

|------------------------------------------------------------------------------|----|

| Tabela 5.2 – Parâmetros dos componentes do LF                                |    |

| Tabela 5.3 – Dimensões dos transistores que compõem o CP                     |    |

| Tabela 5.4 – Resumo das características deste PLL e comparação com trabalhos |    |

| semelhantes                                                                  | 23 |

# LISTA DE SÍMBOLOS, NOMENCLATURAS E ABREVIAÇÕES

PLL: Phase-Locked Loop

VCO: Voltage Controlled Oscillator

LF: Loop Filter CP: Charge Pump

PFD: Phase-Frequency Detector LNA: Low Noise Amplifier SoC: System on Chip

nmos: n-type channel metal-oxide-semiconductor pmos: p-type channel metal-oxide-semiconductor

Vup: Saída do PFD Vdown: Saída do PFD

$\phi_{out}$ : Fase do sinal de saída do VCO

$v_{ctrl}$ : Tensão de controle do VCO

$egin{array}{ll} K_{V\!C\!O}: & {\sf Ganho~do~VCO} \\ I_{C\!P}: & {\sf Corrente~do~CP} \end{array}$

$oldsymbol{\omega_n}$ : Frequência natural de oscilação  $\zeta$ : Coeficiente de amortecimento

AMS: Austria MicroSystems

$^{W_c}$  : Frequência de corte da função de transferência do loop em malha aberta

$w_z$ : Frequência do zero da função de transferência do loop em malha aberta

$w_n$ : Freqüência natural do loop

$egin{array}{ll} R_1: & \operatorname{Primeiro\ resistor\ do\ LF} \\ C_1: & \operatorname{Primeiro\ capacitor\ do\ LF} \\ C_2: & \operatorname{Segundo\ capacitor\ do\ LF} \\ \end{array}$

N: Constante de divisão do divisor

UP: Transistor funcionando como chave para carregar o LF

DW: Transistor funcionando como chave para descarregar o LF

M1: Transistor do CPM2: Transistor do CPM3: Transistor do CPM4: Transistor do CP

VHDL: VHSIC Hardware Description Language INV3: Célula inversor da biblioteca da AMS

CLKINV15: Célula da biblioteca da AMS

W/L: Largura por comprimento do canal do transistor

Wn: Largura do transistor nmos que faz parte do anel do VCO

Ln: Comprimento do transistor nmos que faz parte do anel do VCO

Wp: Largura do transistor pmos que faz parte do anel do VCO

Lp: Comprimento do transistor pmos que faz parte do anel do VCO

Wt: Largura do transistor nmos que faz parte da estrutura de controle do VCO

Lt: Comprimento do transistor nmos que faz parte da estrutura de controle do VCO

Cap: Capacitância do capacitor que faz parte da estrutura de controle do VCO

### 1 INTRODUÇÃO

#### 1.1 DEFINIÇÃO DO PROBLEMA

Receptores são um dos elementos básicos de um sistema de comunicação. Sua função é recuperar a informação que foi enviada por um transmissor através de um canal. Para desempenhar essa função, o receptor precisa demodular o sinal. Para isso, ele necessita gerar internamente um sinal com a mesma frequência que foi utilizada para modulação e transmissão da informação.

Este trabalho propõe o projeto de um Phase-Locked Loop (PLL) para desempenhar a função de sintetizador de frequência no receptor.

#### 1.2 ORGANIZAÇÃO DO TRABALHO

Na Seção 2, uma breve revisão bibliográfica acerca dos temas pertinentes a esse projeto é feita.

A Seção 3 apresenta a metodologia de projeto do PLL e de cada um dos circuitos que o constituem. Especificações, topologias e fluxo de projeto dos circuitos são apresentados nessa seção.

A Seção 4 apresenta detalhes sobre o projeto de cada circuito.

Na Seção 5 são apresentados os resultados dos projetos individuais e da integração do PLL. Os problemas ocorridos, as limitações encontradas no projeto de cada circuito, os circuitos finais desenvolvidos bem como suas simulações funcionais são apresentadas nessa parte.

Por fim, tem-se uma conclusão na Seção 6 a respeito deste trabalho, contendo as impressões sobre o projeto e sugestões para trabalhos futuros e, na Seção 8, estão presentes alguns dados sobre as simulações utilizadas no projeto.

### 2 REVISÃO BIBLIOGRÁFICA

#### 2.1 O RECEPTOR

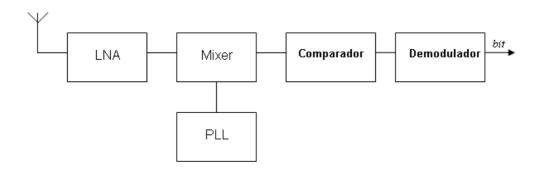

A arquitetura do receptor é apresentada na Figura 2.1. Esse projeto foi criado para receber sinais modulados digitalmente, com esquema de modulação de frequência e codificação Manchester. Pretende-se inserir essa arquitetura em um Sistema em Chip (SoC) para aplicações em rede de sensores sem fio.

O primeiro bloco desse receptor é o LNA. Consiste de um amplificador com alto ganho e baixa figura de ruído. Sua função é amplificar o sinal recebido, porém adicionando o mínimo de ruído. Seu alto ganho e baixa figura de ruído auxiliam para que o ruído acrescentado pelo resto do sistema degrade pouco o sinal que estará sendo recebido e demodulado.

O próximo bloco é o Mixer. Trata-se de um circuito cuja função é realizar o produto entre o sinal recebido pelo LNA e o sinal gerado pelo sintetizador de frequência, transladando o sinal recebido de banda-passante para banda-base. Nessa arquitetura, a função de sintetizador de frequência é desempenhada pelo PLL.

Após ser transladado para banda-base, o sinal passa por um Comparador. O objetivo real desse bloco é condicionar o sinal recebido, transformando-o em um sinal digital, uma onda quadrada com amplitude de 0V a 3.3V.

No Demodulador, ocorre a demodulação propriamente dita. Trata-se de um bloco digital com capacidade de variar a taxa de transmissão e que recebe um sinal digital modulado em frequência e codificado utilizando o esquema Manchester e entregar em sua saída apenas os bits referentes à informação.

Figura 2.1 – Diagrama de blocos do Receptor

### 2.2 PHASE-LOCKED LOOP DEFINIÇÃO E COMPONENTES

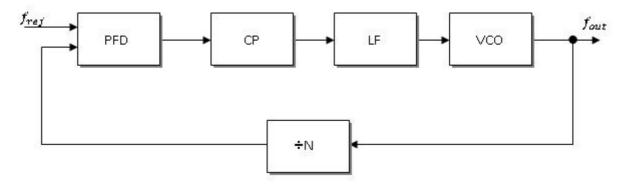

Phase-Locked Loop (PLL) é um sistema em malha fechada com realimentação negativa que utiliza a fase de sinais periódicos como variável. Dentro do receptor, o PLL tem a função de gerar um sinal com uma frequência fixa, o qual será utilizado na demodulação.

O PLL é formado pelos seguintes circuitos: *Voltage Controlled Oscillator* (VCO), *Loop Filter* (LF), *Charge Pump* (CP), *Phase-Frequency Detector* (PFD) e o Divisor de Frequência (Divisor). O funcionamento de cada um desses blocos está explicado nos tópicos seguintes e o posicionamento de cada um deles no loop está descrito na Figura 2.2.

Figura 2.2 – Diagrama de Blocos do PLL

O PFD é responsável por comparar a frequência do sinal gerado pelo VCO com a frequência de um sinal de referência. Como a frequência gerada pelo VCO costuma ser muito maior do que a frequência gerada pela referência, antes de ser comparado pelo PFD, a freqüência do sinal gerado pelo VCO é dividido pelo Divisor até que esteja praticamente igual à frequência de referência e suas fases possam ser comparadas. Após comparar a fase desses dois sinais, aparece em uma das duas saídas do PFD - as quais foram denominadas nesse trabalho de Vup e Vdown – um sinal de erro, um pulso, com largura igual ao tamanho da defasagem entre os dois sinais de entrada que foram comparados. Se a frequência do sinal gerado pelo VCO estiver maior do que a referência, o pulso com a diferença de fase entre os dois aparece na saída Vdown. Se a frequência do sinal gerado pelo VCO estiver menor do que a referência, o pulso aparece na saída Vup.

As saídas do PFD são conectadas ao CP. Se existir um pulso na saída Vup, o circuito do CP injeta corrente nos capacitores do LF para carregá-los. Se existir um pulso na saída Vdown, o CP retira corrente dos capacitores do LF para descarregá-los.

Se os capacitores do LF são carregados, a tensão em sua saída aumenta. Essa tensão é utilizada para controlar a frequência do sinal gerado pelo VCO. Se essa tensão aumentar, a frequência do sinal gerado diminui. Se os capacitores do LF são descarregados, a tensão na saída do filtro diminui. Se essa tensão diminuir, a frequência do sinal gerado pelo VCO aumentará. É dessa forma que o loop controla e estabiliza a frequência do sinal gerado pelo VCO.

#### 2.2.1 VOLTAGE CONTROLLED OSCILLATOR (VCO)

Um oscilador é um sistema que apresenta em sua saída um sinal periódico sem que haja um sinal em sua entrada. Para que isso seja possível, esse sistema deve obedecer ao critério de Barkhausen's [1]. Esse critério define que, considerando um sistema linear em malha fechada descrito no domínio de Laplace:

$$G(s) = \frac{H(s)}{1 - H(s)} \tag{2.1}$$

Se  $|H(s_o)|=1$  e  $\angle H(s_o)=0$  para um determinado  $s_o$ , então esse sistema oscilará com frequência constante. Deve-se observar que esse critério é necessário, porém não suficiente [1].

O VCO é um oscilador cuja frequência gerada pode ser controlada por meio da variação de tensão. Dentre as topologias comumente utilizadas, o VCO em anel terá ênfase nesse trabalho devido à sua simplicidade e sua larga faixa de sintonia [2]. O VCO em anel consiste de um

número ímpar de inversores conectados em série, formando um anel. De acordo com [2], a frequência de oscilação de um anel de inversores é dada pela expressão:

$$f = \frac{1}{2 \times N \times t} \tag{2.2}$$

Onde *N* é o número de estágios de inversores e t é o atraso de cada inversor.

#### 2.2.2 LOOP FILTER (LF)

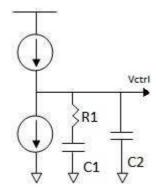

O LF é um filtro responsável por fornecer na entrada do VCO os pulsos de tensão necessários para ajustar o oscilador na frequência correta. Esse filtro é composto por um capacitor em série com um resistor e ambos em paralelo com um segundo capacitor. A função do primeiro capacitor é integrar os pulsos de corrente fornecidos pelo CP. O resistor é colocado em série por questões de estabilidade [1]. O segundo capacitor tem a função de diminuir o efeito ripple adicionado ao loop pelo resistor em série com o primeiro capacitor [1].

#### 2.2.3 CHARGE PUMP (CP)

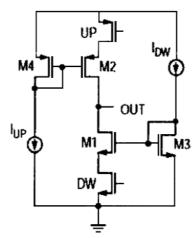

Esse circuito consiste de duas chaves, uma para acrescentar corrente no capacitor do filtro LF e outro para retirar corrente do mesmo capacitor. Essas chaves são feitas com dois transistores, um funcionando como fonte de corrente e outro funcionando como dreno de corrente. O circuito elétrico desse bloco está demonstrado na Figura 2.3.

Figura 2.3 - Circuito do CP com LF

#### 2.2.4 PHASE FREQUENCY DETECTOR (PFD)

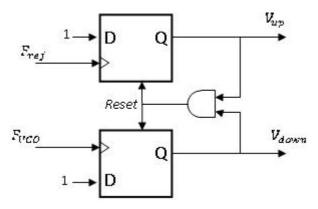

A função desse bloco é comparar a fase do sinal gerado pelo VCO com a fase do sinal gerado pela referência de frequência e gerar dois sinais de erro, Vup e Vdown. O sinal Vup ativa a fonte de corrente do CP, carregando o capacitor do LF para que haja uma "aceleração" no VCO, fazendo com que a fase do sinal gerado se iguale com a fase da referência. O sinal Vdown faz o contrário, ele aciona o dreno de corrente, descarregando o capacitor e "desacelerando" o VCO para que a fase do sinal gerado se iguale à referência. O circuito do PFD está demonstrado na Figura 2.4.

Figura 2.4 - Circuito do PFD

#### 2.2.5 DIVISOR DE FREQUÊNCIA

Geralmente o sinal que é usado como referência de frequência é gerado por um cristal. Esse dispositivo gera frequências na ordem de algumas dezenas de Megahertz. Já a frequência do sinal gerado pelo VCO está próxima de um Gigahertz. Para que o PFD possa comparar corretamente a fase desses dois sinais, a frequência do sinal gerado pelo VCO deve ser reduzida, e essa redução é feita pelo divisor de frequência.

A arquitetura do divisor é simples. Trata-se de uma sequência de flip-flops utilizados assincronamente para divisão da frequência do sinal gerado pelo VCO.

#### ESTUDO DO PLL NO DOMÍNIO s 2.3

Cada elemento que faz parte do loop do PLL pode ser modelado no domínio s. O objetivo dessa modelagem é a observação de determinadas características do loop como largura de banda, estabilidade, etc.

Começando pelo VCO, o mesmo pode ser considerado como um sistema invariante no tempo que possui como sua entrada a tensão de controle e como sua saída, a fase de um sinal periódico [1]. Dessa forma, tem-se que:

$$\phi_{out} = K_{VCO} \int v_{ctrl} dt \tag{2.3}$$

que no domínio s se transforma em

$$\frac{\phi_{out}}{v_{ctrl}}(s) = \frac{K_{VCO}}{s} \tag{2.4}$$

Onde,  $\phi_{out}$  é a fase, variável de saída do VCO,  $K_{VCO}$  é o ganho do VCO, calculado como  $K_{VCO} = \frac{frequência}{tensão}$  (2.5)

$$K_{VCO} = \frac{frequência}{tensão} \tag{2.5}$$

e  $v_{ctrl}$  é a tensão de controle, variável de entrada do VCO. Observa-se que para alterar a fase de saída do VCO, deve-se alterar a frequência do sinal gerado pelo mesmo. Para entender melhor esse comportamento, suponha que o VCO esteja gerando um sinal com mesma frequência que a referência, mas com uma diferença de fase finita. Nessa situação, a tensão de controle alteraria a frequência do VCO de modo a aumentá-la ou diminuí-la, de acordo com a necessidade, para fazer com que a diferença de fase fosse nula.

A modelagem do PFD, CP e LF é feita em conjunto. Do funcionamento desses três blocos, observa-se que o PFD gera pulsos com largura igual à diferença de fase entre a referência e a fase do sinal gerado pelo VCO. Esses pulsos ativam o CP, que insere carga no capacitor do LF.

O LF é modelado como um filtro de primeira ordem, tendo a seguinte função de transferência:

$$\frac{v_{ctrl}}{I_{CP}}(s) = \frac{1 + sR_1C_1}{sC_1}$$

(2.6)

Observa-se que o segundo capacitor do LF foi ignorado nessa modelagem. Essa aproximação pode ser feita se o valor desse segundo capacitor for mantido entre 10% e 20% do valor do primeiro capacitor [1]. Nessa situação, a filtragem causada por esse capacitor estaria atuando em frequências mais altas, fora da banda de atuação do PLL.

Dessa forma, tem-se que, para um instante de comparação e com uma aproximação linear, a função de transferência desses três blocos resulta em:

$$\frac{v_{ctrl}}{\Delta \phi}(s) = \frac{I_{CP}}{2\pi} \cdot \frac{1 + sR_1C_1}{sC_1}$$

(2.7)

Onde  $I_{\mathit{CP}}$  é a corrente que carrega o capacitor do LF

Finalmente, a função de transferência do loop aberto é dada por:

$$\frac{\phi_{out}}{\Delta \phi}(s) = \frac{I_{CP}}{2\pi} \cdot \frac{(1 + sR_1C_1)}{sC_1} \cdot \frac{K_{VCO}}{s}$$

(2.8)

Observa-se que se trata de um sistema de segunda ordem com dois pólos na origem e um

zero em

$$s = \frac{-1}{R_1 C_1}$$

.

Fechando-se a malha e adicionando o divisor de frequência no caminho de realimentação, tem-se a seguinte função de transferência em malha fechada:

$$\frac{\phi_{out}}{\Delta\phi}(s) = \frac{\frac{I_{CP}K_{VCO}}{2\pi C_1^2 R_1} (1 + sR_1C_1)}{s^2 + s\frac{I_{CP}K_{VCO}R_1}{2\pi N} + \frac{I_{CP}K_{VCO}}{2\pi C_1N}}$$

(2.9)

Como a função de transferência do loop fechado é um sistema de segunda ordem, podemse deduzir as seguintes relações:

$$\omega_n = \sqrt{\frac{I_{CP} K_{VCO}}{2\pi C_1 N}} \tag{2.10}$$

$$\zeta = \frac{R_1}{2} \sqrt{\frac{I_{CP} K_{VCO} C_1}{2\pi N}}$$

(2.11)

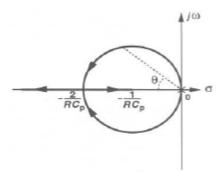

O Lugar Geométrico das Raízes para a função de transferência do loop aberto esta descrito na Figura 2.5.

Figura 2.5 – Lugar Geométrico das Raízes para a função de transferência do loop aberto

Pode-se notar que, à medida que há um aumento em  $K_{VCO}I_{CP}$ , os pólos em malha fechada se deslocam em um círculo da origem em direção ao zero de malha aberta, ou seja, o sistema continua estável, mesmo com um aumento no seu ganho.

#### 3 METODOLOGIA

#### 3.1 O PLL

O primeiro passo antes da execução do projeto do PLL é definir suas especificações e as especificações para todos os blocos que fazem parte da malha de realimentação. As especificações para o PLL serão descritas nessa seção, enquanto as especificações para cada bloco serão descritas em suas respectivas seções.

Tem-se o seguinte conjunto de especificações iniciais para o PLL:

• Frequência de operação: 920MHz

• Frequência da referência: 20MHz

• Número de canais: 1

• Banda de cada canal: 1MHz

• Tecnologia: AMS C35B4C3 3.3V

Definidas as especificações para o PLL, serão definidas especificações para cada um dos blocos separadamente, mas observando não só seu funcionamento individual como também suas conexões com os outros blocos vizinhos, para que todos possam funcionar em conjunto dentro do PLL.

O projeto elétrico dos blocos, simulações necessárias, leiaute e verificações pertinentes serão todas feitas utilizando as ferramentas de projeto de circuito integrado da CADENCE. No anexo, ao final desse trabalho, estão descritas as simulações que foram utilizadas para validação dos circuitos que serão projetados nesse trabalho.

#### 3.2 O VCO

Primeiramente define-se o conjunto de especificações para o projeto do VCO:

• Frequência do sinal de saída: 920MHz

• Número de saídas: 2 saídas defasadas de 180° entre si

Tensão de saída do sinal: 0V a 3.3V

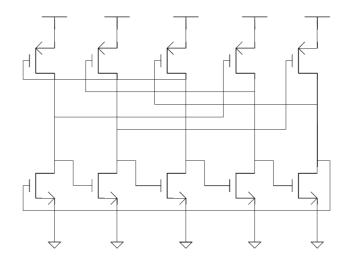

• Tensão de saída do dc: 1.65V

Com essas especificações definidas, define-se o projeto elétrico do VCO. A topologia escolhida foi a descrita em [8]. Em resumo, essa topologia é capaz de aumentar em até 50% a frequência de oscilação de um oscilador em anel se comparado com o mesmo anel construído de maneira convencional. Outro motivo para a escolha dessa topologia foi o fato de que, apesar de o sinal de saída ser gerado por inversores, e, portanto por células digitais, este possui um formato mais próximo de uma senóide do que de uma onda quadrada. O esquemático do circuito elétrico pode ser visualizado nas Figuras 3.1 e 3.2.

Figura 3.1 – Esquemático do VCO.

Figura 3.2 – Esquemático do VCO com carga funcionando como controle.

#### 3.3 O LF

O LF terá a topologia descrita no Tópico 2.1.2. Como explicitado, esse filtro consta de um capacitor em série com um resistor e ambos em paralelo com um segundo capacitor. A sequência de cálculos que serão utilizados para dimensionar o LF foi baseada em [9] e estão listados a seguir:

# 1. Determinação da largura de banda do loop e igualá-la à frequência de corte do loop em malha aberta, $^{\mathcal{W}_c}$ .

É necessário observar nessa etapa que a largura de banda do loop deve assumir um valor em torno de 10% da frequência de referencia [1], [2]. Essa medida visa a garantir margem de fase aceitável ao sistema no pior caso, ou seja, considerando-se variações de dimensões de componentes, de processo, de tensão de alimentação, etc.

# 2. Escolher uma frequência para o zero compreendida entre um décimo e um quarto da frequência de corte do loop, isto é:

$$w_c/10 \le w_z \le w_c/4 \tag{3.1}$$

Esses limites para a frequência do zero têm como objetivo garantir uma boa margem de fase para o sistema [2].

#### 3. Calcular a frequência natural do loop

Se a frequência do zero for mantida dentro dos limites estabelecidos pela etapa anterior, então a frequência natural pode ser calculada utilizando-se a expressão [2]:

$$W_c \approx \frac{w_n^2}{W_z} \tag{3.2}$$

#### 4. Calcular a capacitância do primeiro capacitor.

Após calcular a frequência natural do loop, pode-se calcular o valor da capacitância do primeiro capacitor através da expressão [2]:

$$w_n = \sqrt{\frac{I_p K_{VCO}}{2\pi C_1 N}} \tag{3.3}$$

#### 5. Calcular a resistência do resistor

Para encontrar o valor da resistência do resistor, utiliza-se a expressão:

$$w_z = \frac{2\pi}{R_1 C_1} \tag{3.4}$$

# 6. Calcular o valor da constante de amortecimento para verificar se esta assumiu um valor acima de 0.7

Esse cálculo tem como objetivo verificar se o sistema esta estável. Se não estiver, então se deve escolher outro valor para a frequência do zero e, para essa nova frequência, recalcular o valor da capacitância e da resistência. O calculo do valor da constante de amortecimento é feito utilizando-se a expressão [2]:

$$\zeta = \frac{R_1}{2} \sqrt{\frac{I_{cp} K_{VCO} C_1}{2\pi N}}$$

(3.5)

#### 7. Verificar o limite de estabilidade do sistema

Esse cálculo é feito utilizando-se a função de transferência em malha aberta do sistema, o qual já possui todas as constantes calculadas, e calculando-se o gráfico de Bode para averiguação da margem de fase do sistema.

# 8. Atribuir valor da capacitância do segundo capacitor como sendo entre 10% e 20% da capacitância do primeiro capacitor

Nessa etapa, basta apenas escolher um valor para o segundo capacitor, desde que esteja dentro dos limites mencionados. Se esses limites forem observados, então se pode considerar que a função de transferência do filtro é de segunda ordem e não de terceira ordem [1], [2]. Assim, todas as equações utilizadas nos passos anteriores ainda são validas.

#### 3.4 O CHARGE PUMP

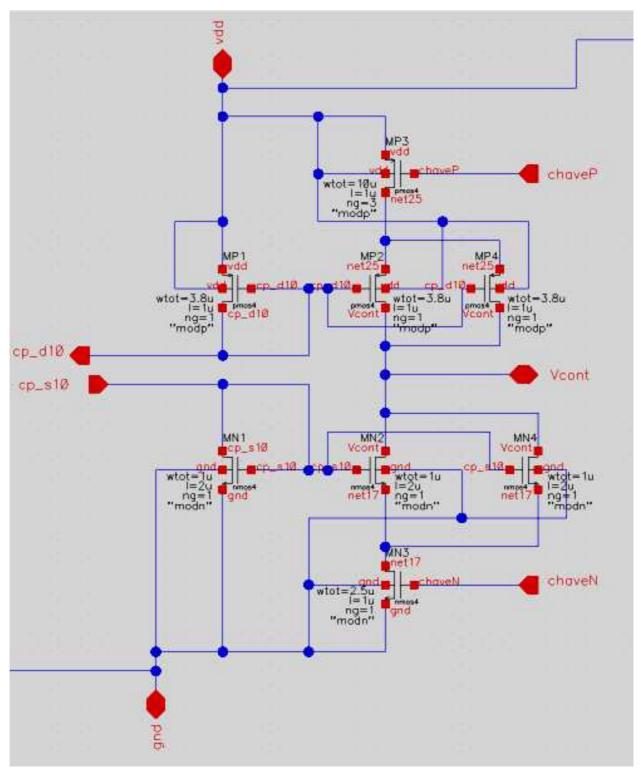

Como mencionado no Tópico 2.1.3, o Charge Pump (CP) é visto como uma fonte ou dreno de corrente controlado por sinais de tensão de saída do PFD. Sua função é fornecer corrente para o capacitor do LF ou retirar corrente deste. O esquemático da arquitetura escolhida é mostrado na Figura 3.3. Esse circuito é constituído por dois espelhos de corrente (polarizados por uma referência de corrente) cujas saídas são controladas por chaves de transistores MOS.

Figura 3.3 - Esquemático do Charge Pump.

Na Figura 3.3, IUP e IDW são os circuitos de dreno e fonte de corrente do bloco Referência de Corrente [16]. Os transistores UP e DW funcionam como chaves que permitem carregar ou descarregar o filtro LF conectado na saída OUT. As portas dos transistores UP e DW são conectadas às respectivas saídas Vup e Vdown do PFD.

O funcionamento do circuito CP é simples. Quando o transistor UP é acionado (transistor DW cortado) com 0V na porta, passa a conduzir uma corrente através de M2, que são aplicados ao filtro LF, aumentando a tensão em OUT. Quando o transistor DW é acionado (transistor UP em corte) a corrente através de M1 é drenada, diminuindo a tensão em OUT.

#### 3.5 O PFD

O PFD é um bloco simples. Suas especificações resumem-se a:

• Tensão dos sinais de entrada: 0V a 3.3V

Para seu projeto, será feita uma descrição de seu comportamento em VHDL e o código resultante será sintetizado utilizando ferramentas de síntese da CADENCE.

#### 3.6 O DIVISOR DE FREQUÊNCIA

A única especificação para o divisor é a seguinte:

• Constante de divisão de frequência: 46

Seu comportamento também será descrito em VHDL e sintetizado utilizando ferramentas de síntese da CADENCE.

#### 4.1 PROJETO DO VCO

O projeto elétrico do VCO consistiu de inversores ligados como descrito em [8], mais estruturas de controle inseridos entre cada inversor. Cada estrutura de controle, ou carga, consiste de um transistor nmos em série com um capacitor. A tensão de controle do VCO entra no gate de cada transistor nmos das estruturas de controle. Dessa maneira, variando a tensão de controle, pode-se variar a carga entre cada inversor, variando dessa maneira o atraso entre cada inversor, por fim variando a frequência de oscilação do VCO.

Utilizando o ambiente de simulação de circuitos da CADENCE, foram realizadas iterações para otimizar as dimensões dos componentes do circuito, partindo das dimensões descritas em [8].

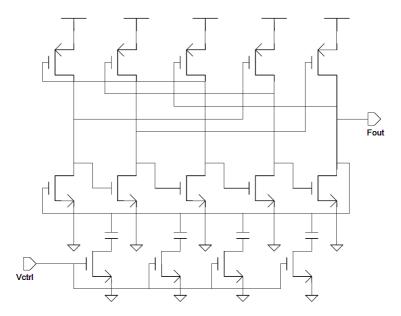

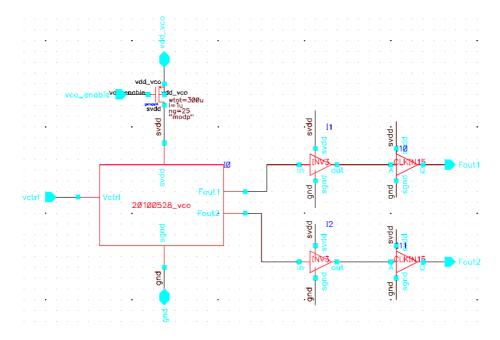

Para corresponder a uma exigência do Mixer, foram adicionadas a cada uma das saídas do VCO uma inversora INV3 [17] e uma célula CLKINV15 [18], ambas da biblioteca da AMS, para servirem como buffers, possibilitando que a tensão do sinal de saída atendesse a uma das especificações do VCO e variasse de 0V a 3.3V, o que não acontece com um anel contendo cinco inversores nessa arquitetura. Outro motivo para a adição dos buffers foi a necessidade de isolar o VCO e impedir que seu funcionamento fosse dependente do circuito conectado a ele.

Foi previsto que, como o VCO é bastante sensível a variações de parâmetros de fabricação, provavelmente, após a fabricação, sua faixa de frequências sintetizáveis seria reduzida para frequências abaixo das previstas por simulações. Para evitar que o VCO não seja capaz de sintetizar a frequência requerida, sua alimentação foi individualizada. Planeja-se com isso poder variar a tensão de alimentação de 3.3V ate 5V e por consequência aumentar a faixa de frequências sintetizáveis pelo VCO, já que essa faixa de frequências também é função da tensão de alimentação.

Alem dessas necessidades, o projeto do VCO precisou incluir um meio de habilitação e desabilitação de seu funcionamento. Para atender a esse requisito, foi adicionado um transistor pmos com dimensão W/L de 300um/1um entre a alimentação e o VCO, o qual funciona como chave, ligando e desligando o oscilador quando uma tensão de 0V e 3.3V respectivamente é aplicada nessa entrada.

#### 4.2 PROJETO DO LOOP FILTER

Os projetos do VCO e do CP possibilitaram que alguns parâmetros de interesse para o projeto do filtro fossem definidos. Esses parâmetros são o ganho do VCO e a corrente do CP. Conhecidos esses parâmetros, realizou-se a sequência de cálculos para o projeto do filtro. A sequência de cálculos citada na metodologia do projeto do LF foi implementada em um roteiro para então utilizar a ferramenta MATLAB para realização das contas e otimização dos parâmetros. Este roteiro encontra-se no anexo.

#### 4.3 PROJETO DO CHARGE PUMP

O ponto de partida para dimensionamento do circuito é a corrente de carga/descarga. Tendo encontrado este parâmetro, utiliza-se um fator de conversão igual a 0,5 para dimensionamento dos espelhos de corrente. Para o correto funcionamento deste bloco é

necessário que as correntes de carga e descarga do filtro sejam iguais, o que é garantido pela igualdade entre IUP e IDW e pelo correto dimensionamento dos espelhos de corrente formados por M4/M2 e M1/M3.

Sabendo que esse tipo de espelho é projetado para um ganho máximo igual a 4, sem que haja distorção significativa, estima-se a corrente IUP (e consequentemente IDW) igual a 10 uA. Sabendo a relação de aspecto dos espelhos de corrente é 2 estima-se M4 e M3 usando a equação de primeira ordem da corrente de dreno para transistores MOS na saturação. Em seguida dimensiona-se, por tentativa e erro, UP e DW de forma que tenham o maior W possível.

#### 4.4 PROJETO DO PFD

O projeto do PFD foi simples. Partindo-se da descrição funcional do PFD feita em VHDL, a síntese do circuito foi realizada utilizando-se as ferramentas de síntese da CADENCE.

#### 4.5 PROJETO DO DIVISOR

O projeto do Divisor também foi simples. Assim como o projeto do PFD, partiu-se de uma descrição comportamental em VHDL do circuito, levando em consideração as especificações definidas previamente e, utilizando-se as ferramentas de síntese da CADENCE, o circuito foi sintetizado.

#### **5 RESULTADOS**

#### 5.1 VCO

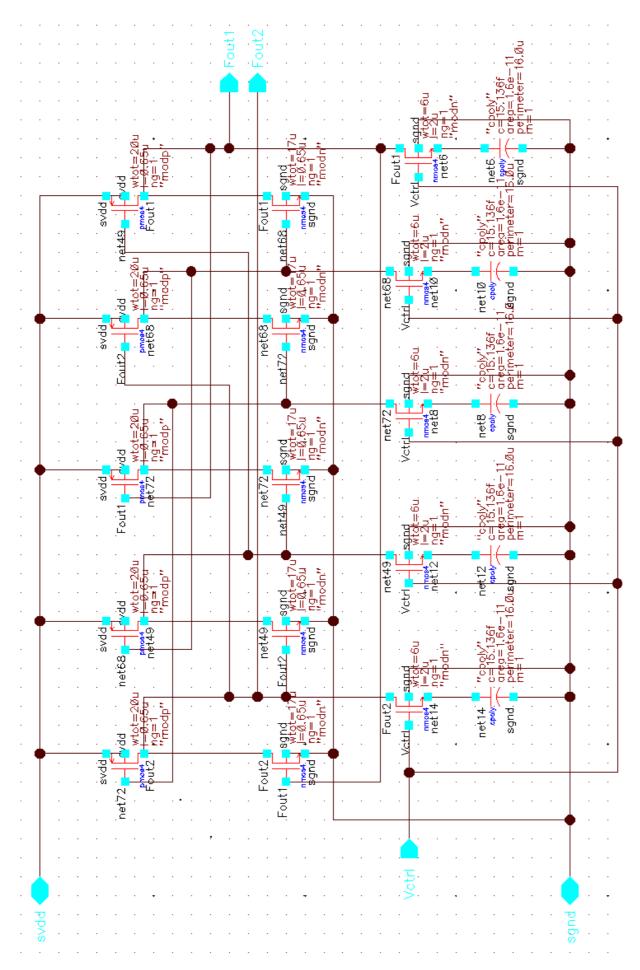

Durante o projeto do VCO, verificou-se que as capacitâncias parasitas degradavam consideravelmente o desempenho do circuito. Uma estratégia para tentar reduzir essas capacitâncias parasitas foi o projeto do VCO contendo apenas cinco estágios de inversores e aproximar os componentes o máximo possível, diminuindo largura e comprimento de trilhas e por consequência, diminuindo as capacitâncias parasitas. Outra estratégia foi o superdimensionamento do circuito elétrico para que, mesmo com a redução das frequências sintetizáveis devido às capacitâncias parasitas, o circuito do VCO com parasitas extraídos fosse capaz de sintetizar a frequência de interesse. Foi feito então um redimensionamento do circuito elétrico para que este sintetizasse frequências próximas de 2GHz e não mais próximas da frequência de interesse. A simetria também foi um quesito observado, já que esta auxilia na redução do ruído de fase inserido por esse circuito no sinal gerado.

As dimensões finais obtidas estão listadas na Tabela 5.1. Deve-se considerar que Wn, Ln, Wp, Lp referem-se às dimensões dos transistores nmos e pmos, respectivamente, que fazem parte dos inversores. Já Wt e Lt referem-se às dimensões dos transistores nmos utilizados como carga de controle, e Cap refere-se à capacitância dos capacitores que também fazem parte da estrutura de carga de controle.

| DIMENSÃO | VALOR |  |

|----------|-------|--|

| Wn       | 17um  |  |

| Ln       | 650nm |  |

| Wp       | 20um  |  |

| LP       | 650nm |  |

| Wt       | 6um   |  |

| Lt       | 2um   |  |

| Cap      | 15fF  |  |

Tabela 5.1 – Dimensões dos componentes do VCO

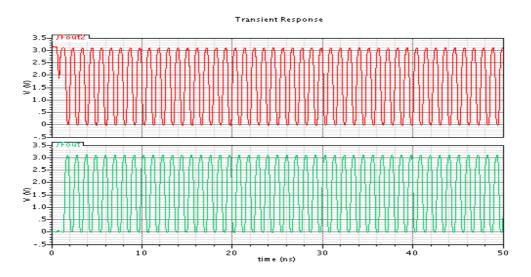

O esquemático do VCO é apresentado na Figura 5.1 e, na Figura 5.2, é possível observar o VCO juntamente com uma célula INV3 e uma célula CLKINV15 conectadas em cada uma de suas duas saídas para funcionarem como buffers. Também pode ser visto o transistor pmos funcionando como chave de liga/desliga, conectado entre a alimentação externa e o VCO. O funcionamento do projeto elétrico do VCO foi validado utilizando as ferramentas de simulação da CADENCE. Realizando-se a simulação transiente no circuito do VCO, observou-se o comportamento mostrado na Figura 5.3. Nessa figura pode-se observar a defasagem de 180° entre as duas saídas.

Figura 5.1 - Esquemático do VCO com duas saídas e cinco estágios

$\label{eq:figura} Figura~5.2-Esquemático~do~VCO~com~o~transistor~pmos~funcionando~como~chave~e~uma~INV3~e~uma~CLKINV15~em~cada~saída.$

Figura 5.3 – Saídas do VCO. Pode-se observar a defasagem de 180° entre elas.

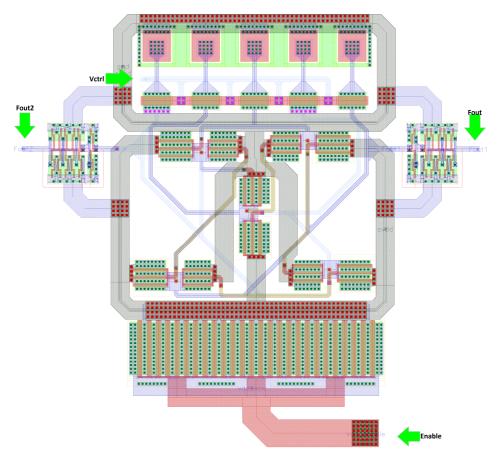

Após validado o funcionamento do circuito elétrico, iniciou-se o leiaute do VCO. O leiaute do circuito é apresentado na Figura 5.4.

Figura 5.4 – Leiaute do VCO com cinco estágios, pmos funcionando como chave liga/desliga e uma INV3 e uma CLKINV15 em cada saída.

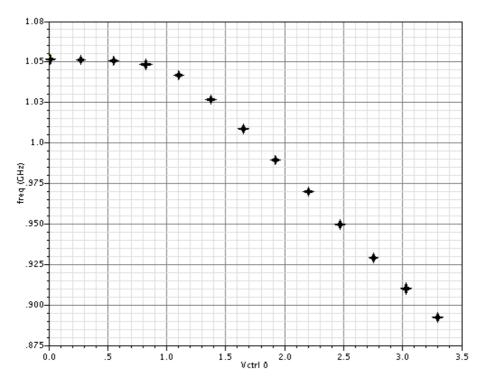

Após a extração dos parasitas desse leiaute, foi realizada uma simulação para verificar o funcionamento do circuito. O resultado pode ser visto na Figura 5.5.

Figura 5.5 – Curva característica do VCO com cinco estágios, Enable e uma INV3 e uma CLKINV15 em cada saída.

Como pode ser verificado na Figura 5.5, o circuito do VCO é capaz de sintetizar a frequência de interesse. Obtida a curva característica, calculou-se o ganho do VCO partindose da linearização em torno do ponto próximo de 920MHz:

$$K_{VCO} = \frac{frequência}{tensão} = \frac{\Delta Y}{\Delta X} = \frac{(950MHz - 910MHz)}{(2.5V - 3.0V)} = 80 MHz/V$$

(5.1)

#### 5.2 LOOP FILTER

Após realizados os cálculos descritos na metodologia do LF para dimensionamento do mesmo, os seguintes parâmetros apresentadas na Tabela 5.2 foram obtidos.

|              | 1                      |  |  |

|--------------|------------------------|--|--|

| COMPONENTE   | PARÂMETRO              |  |  |

| Resistor     | $1.5 \mathrm{M}\Omega$ |  |  |

| 1° Capacitor | 1pF                    |  |  |

| 2° Capacitor | 400fF                  |  |  |

Tabela 5.2 – Parâmetros dos componentes do LF

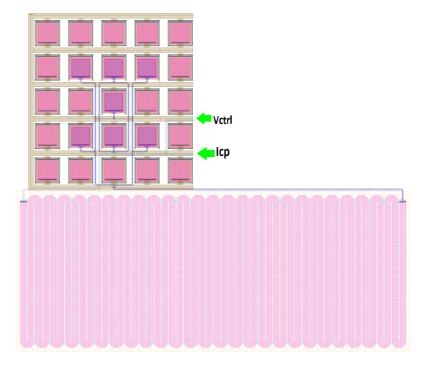

Depois que as dimensões dos capacitores e do resistor foram determinadas, o leiaute do LF foi desenvolvido. Cada capacitor foi dividido em conjuntos de capacitores de 200fF conectados em paralelo. A intenção ao se fazer isso é evitar que, caso ocorra algum dano no local onde se encontram os capacitores, o circuito não fique inoperante, já que restariam alguns capacitores menores ainda funcionais. Esses capacitores conectados em paralelo foram rodeados por outros capacitores *dummy*, para reduzir a variação de parâmetros devido à fabricação [5], [6], [7]. O leiaute do filtro pode ser observado na Figura 5.6.

Figura 5.6 – Leiaute do LF.

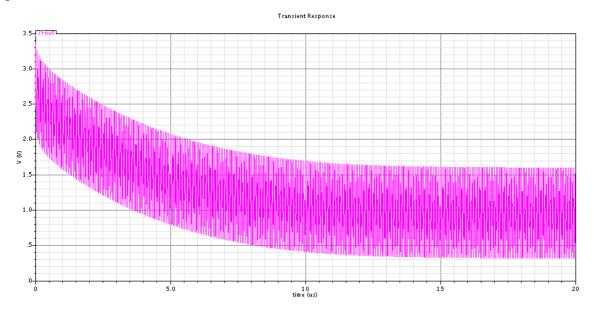

Para verificar o tempo de estabilização do filtro, foi realizada uma simulação transiente desse circuito. Como entrada, tem-se uma fonte de corrente simulando o CP. Como saída, o circuito possui uma carga capacitiva simulando a entrada do VCO. O resultado dessa simulação é apresentado na Figura 5.7. Observa-se que o tempo de assentamento do LF está próximo de 20us.

Figura 5.7 - Simulação transiente do LF

Apesar de ter sido possível utilizar a sequência de cálculo descrita para dimensionar os componentes do LF, a mesma não se mostrou muito adequada para esta função. Existem muitos parâmetros a serem definidos que não possuíam especificação. Esses valores foram então estimados e a sequencia de cálculos realizada para verificar se a estimativa estava adequada. Se não estivesse, novamente esses parâmetros não especificados deveriam ser estimados e a sequencia de cálculos refeita.

#### 5.3 CHARGE PUMP

Após realizadas a iterações, cálculos, estimações e ajustes descritas na parte de projeto do CP, as dimensões obtidas de todos os transistores estão na Tabela 5.3.

| TRANSISTOR | W/L(µm) |

|------------|---------|

| M1         | 1/2     |

| M2         | 3,8/1   |

| M3         | 1/2     |

| M4         | 3,8/1   |

| UP         | 10/1    |

| DW         | 2,5/1   |

Tabela 5.3 - Dimensões dos transistores que compõem o CP

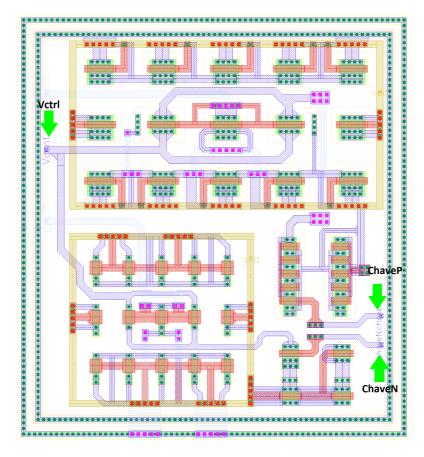

O esquemático é apresentado na Figura 5.8 e o leiaute, na Figura 5.9. Observam-se novamente componentes *dummy* adicionados ao leiaute. Como mencionado em [5], [6] e [7], trata-se de uma técnica utilizada para diminuir a variação do comportamento do circuito às variações de parâmetros de fabricação.

Figura 5.8 – Esquemático do CP.

Figura 5.9 – Leiaute do circuito do CP.

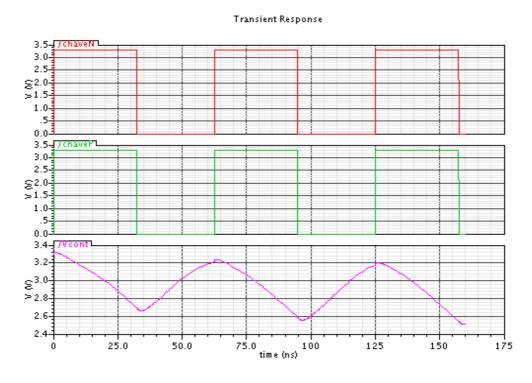

O teste do circuito CP consiste em habilitar cada uma das chaves transistorizadas separadamente simulando o comportamento do PFD e verificar a tensão de controle sobre o filtro. A carga utilizada é o circuito do LF. O resultado da simulação do CP é apresentado na Figura 5.10.

Figura 5.10 – Simulação do CP

#### 5.4 PFD E DIVISOR

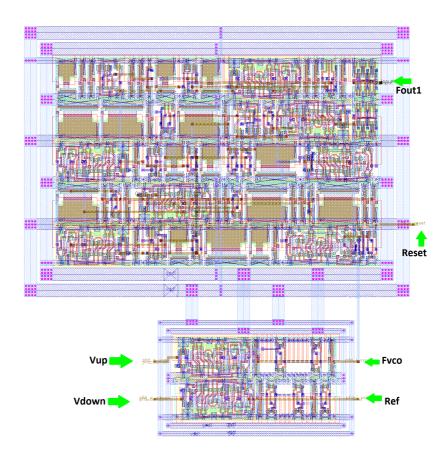

Após a síntese lógica e física dos códigos descritivos dos circuitos do PFD e do Divisor, os leiautes obtidos são apresentados na figura 5.11.

Figura 5.11 – Leiaute do Divisor (acima) juntamente com o leiaute do PFD (abaixo)

#### 5.5 PLL COMPLETO

Finalizada as etapas de projeto de cada um dos circuitos que compõem o PLL, a integração de todos eles foi iniciada. Cada circuito foi planejado pensando não somente em seu correto funcionamento, mas também na sua capacidade de continuar funcionando corretamente quando conectado com os outros circuitos.

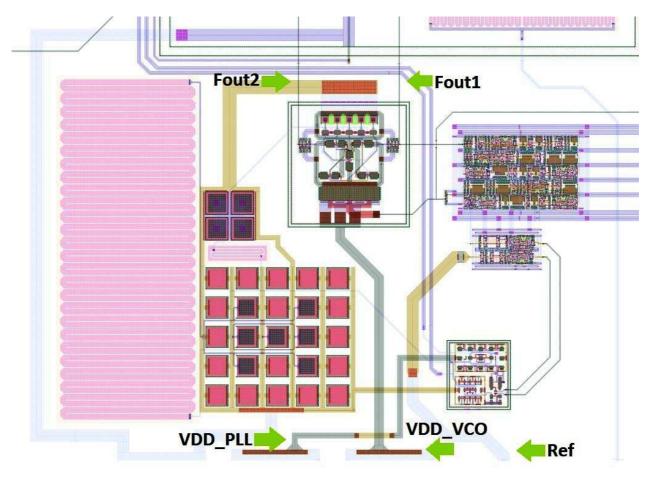

O resultado da integração pode ser observado na 5.12.

Figura 5.12 – Leiaute do PLL

Ao redor dos componentes que produzem muito ruído, como o VCO e o CP, foram adicionados anéis de guarda para que o ruído produzido por esses circuitos não interferisse nos outros circuitos.

Observa-se no leiaute que, em serie com o LF, foi adicionado mais outro filtro. Essa modificação foi necessária, já que o projeto inicial do PLL previa uma frequência de referência de 16MHz, e somente após a finalização do projeto do PLL essa frequência foi alterada para 20MHz. Decidiu-se por apenas adicionar outro filtro em serie com o LF, ao invés de refazer o projeto deste.

Na Tabela 5.4 tem-se em resumo as características deste PLL, bem como uma comparação com trabalhos semelhantes.

| PARÂMETRO                                      | ESTE PLL         | REFERENCIA [19]  | REFERENCIA [20] |

|------------------------------------------------|------------------|------------------|-----------------|

| Processo                                       | 0.35μm 3.3V CMOS | 0.35μm 3.3V CMOS | 0.6μm CMOS      |

| Corrente do CP (Icp)                           | 20μΑ             | -                | -               |

| Faixa de Frequências<br>Sintetizáveis pelo VCO | 890-1050MHz      | 880-1648 MHz     | 750-1200GHz     |

| Consumo                                        | 25mW             | 109mW            | 30mW            |

Tabela 5.4 – Resumo das características deste PLL e comparação com trabalhos semelhantes

### **6 CONCLUSÕES**

Nesse trabalho foi desenvolvido o projeto completo de um *Phase-Locked Loop* (PLL) em tecnologia 0.35µm 3.3V CMOS funcionando em 920MHz, com consumo simulado de 25mW para um SoC.

O circuito do *Voltage Controlled Oscilator* (VCO), projetado utilizando-se uma arquitetura de VCO em anel com compensação de atraso, conseguiu sintetizar a frequência especificada de 920MHz – na faixa de 890-1050MHz - com ganho de 80MHz/V resolução simulada de aproximadamente 100KHz.

O projeto do PLL resultou em circuitos que são capazes de operar dentro das especificações definidas e que possuem características semelhantes a outros trabalhos realizados, como pode ser visto na Tabela 5.4.

Para trabalhos futuros, deseja-se definir uma metodologia de projeto mais adequada para o Loop Filter (LF), incluindo novos parâmetros pertinentes e talvez alterando a sequência de cálculos necessários ao seu correto dimensionamento. Pretende-se também utilizar outra topologia de oscilador, mais eficiente em termos de ganho e faixa de operação, menos sensível a variações de parâmetros e com menor consumo de potência. Os circuitos do Divisor e do PFD, por serem ambos digitais, poderão ser sintetizados em conjunto, formando um único bloco digital.

### 7 REFERÊNCIAS BIBLIOGRÁFICAS

- [1]BEHZAD, Razavi. *RF MICROELECTRONICS*. Los Angeles, United States of America: Prentice Hall, 1998.

- [2] LEE, Thomas H. *THE DESIGN OF CMOS RADIO-FREQUENCY INTEGRATED CIRCUITS*. United Kingdom: Cambridge University Press, 1998.

- [3]MAK,Pui-In; U,Seng-Pan; MARTINS; Rui Paulo. *ANALOG-BASEBAND ARCHITECTURES AND CIRCUITS FOR MULTISTANDARD AND LOW-VOLTAGE WIRELESS TRANSCEIVERS*. The Netherlands: Springer, 2007.

- [4]SHU,Keliu; SINENCIO,Edgar Sánchez. *CMOS PLL SINTHESIZERS: Analysis and Design*. The United States of America: Springer, 2005.

- [5] SAINT, Christoper; SAINT, Judy. *IC MASK DESIGN: Essential Layout & Techniques*. New York, United States of America: McGraw-Hill, 2002.

- [6] CLEIN, Dan; SHIMOKURA, Gregg. CMOS IC LAYOUT: Concepts, Methodologies and Tools. Osford: Newnes, 2000.

- [7] HASTINGS, Alan. *THE ART OF ANALOG LAYOUT*. New Jersey, United States of America: Prentice Hall, 2001.

- [8] LEE, Seog-Jun; KIM, Beomsup; LEE, Kwyro. *A NOVEL HIGN-SPEED RING OSCILLATOR FOR MULTIPHASE CLOCK GENERATION USING NEGATIVE SKEWED DELAY SCHEME*. IEEE Journal of Solid-State Circuit. Vol 32 NO 2, pp 289-291. 1997.

- [9]SOARES,Rafael Rodrigues Pereira. SINTETIZADOR DE FREQUENCIAS EM TECNOLOGIA CMOS PARA UM TRANSCEPTOR DE RF A 900MHz EM UM SISTEMA EM CHIP. 2005. Dissertação de Mestrado em Engenharia Elétrica Faculdade de Engenharia Elétrica, Universidade de Brasília, Brasília, 2005.

- [10]RHEE, Woogeun. *DESIGN OF HIGH PERFORMANCE CMOS CHARGE PUMPS IN PHASE-LOCKED*. IEEE International Symposium on Circuits and Systems: NewPort Beach-CA, pp. II-545-548, 1999.

- [11] LATHI, B P. *MODERN DIGITAL AND ANALOG COMMUNICATION SYSTEMS*. New York, United States of America: Osford University Press, 1998.

- [12] AUSTRIAMICROSYSTEMS. http://www.austriamicrosystems.com

- [13] BAKER,R Jacob; LI, Harry W; BOYCE, David E. *CMOS: CIRCUIT DESIGN, LAYOUT, AND SIMULATION*. New York, United States of America: Baker, 1998.

- [14] NISE, Norman S. CONTROL SYSTEMS ENGINEERING, Danvers, United States of America: Wiley, 2004.

- [15]BEHZAD, Razavi. *DESIGN OF ANALOG CMOS INTEGRATED CIRCUITS*. Singapore: McGraw-Hill International Edition, 2001.

- [16]ARAUJO, Genival Mariano de. CONVERSOR TENSÃO-CORRENTE EM TECNOLOGIA CMOS PARA UM CONVERSOR ANALÓGICO/DIGITAL DE UM SISTEMA EM CHIP. 2008. Dissertação de Mestrado em Engenharia Elétrica Faculdade de Engenharia Elétrica, Universidade de Brasília Brasília, 2008.

- [17] http://asic.austriamicrosystems.com/databooks/c35/databook\_c35\_33/INV3.html

- [18] http://asic.austriamicrosystems.com/databooks/c35/databook\_c35\_33/CLKIN15.html

- [19] SUN, Lizhong; KWASNIEWSKI, Tadeusz A. A 1.25-GHz 0.35um MONOLITHIC CMOS PLL BASED ON A MULTIPHASE RING OSCILLATOR. Journal of Solid-State Circuit., Vol 36, NO. 6, pp 910-916, June 2001.

- [20] PARK, Chan-Hong; KIM, Beomsup. *A LOW-NOISE 900MHz VCO IN 0.6 um CMOS.* Journal of Solid-State Circuit. Vol 34 NO. 5, pp 586-591. May 1999.

#### 8 ANEXOS

#### 8.1 SIMULAÇÃO TRANSIENTE

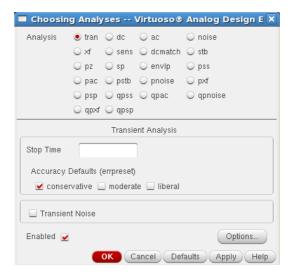

A simulação transiente serve para observar o comportamento do circuito com o passar do tempo. A caixa de diálogo dos ajustes dessa simulação é apresentada na Figura 8.1.

Figura 8.1 – Caixa de diálogo da Simulação Transiente.

O único ajuste necessário a esse projeto é o "Stop Time", o qual define o tempo de simulação transiente, o que vai depender da necessidade da simulação.

#### 8.2 SIMULAÇÃO PSS

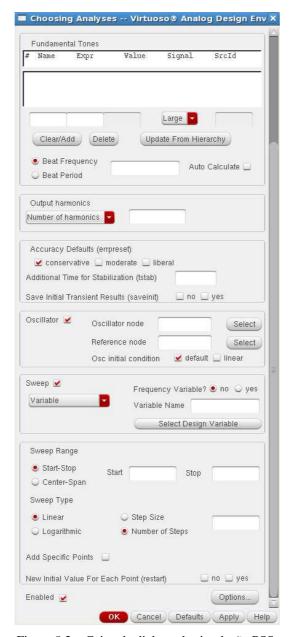

A simulação PSS simula o comportamento do circuito no domínio da frequência. Além disso, é possível variar alguma variável de simulação e observar o comportamento da saída do circuito na frequência para os valores que essa variável assumir. A caixa de dialogo é mostrada na Figura 8.2.

Figura 8.2 – Caixa de dialogo da simulação PSS.

O primeiro ajuste a ser feito é o "Beat Frequency". Esse ajuste indica uma estimativa para a frequência do sinal de saída que será calculado pelo simulador. Como se trata de um cálculo interativo, quanto mais próximo esse valor for da frequência do sinal de saída, mais fácil será a convergência dos cálculos.

O próximo ajuste é o "Number of Harmonics". Nesse trabalho, apenas um harmônico foi importante de ser analisado.

No parâmetro "Additional Time for Stabilization" escolhe-se um valor o qual o simulador vai esperar para que o circuito estabilize. Somente após esse tempo o simulador começa a realizar os cálculos.

No parâmetro "Oscillator node" escolhe-se no esquemático do circuito um nó por onde passe o sinal cuja frequência se deseja observar. Esse nó é referenciado ao nó indicado no parâmetro "Reference node".

Depois de se selecionar a caixa "Sweep", deve-se escolher a variável de simulação a qual se deseja que o simulador altere o valor. Os próximos parâmetros a serem definidos são "Sweep

Range", onde se deve indicar qual o valor inicial e qual o valor final que a variável de simulação vai assumir, "Sweep Type", onde se escolheu "Linear" e, depois de selecionar a opção "Number of Steps", define-se quantos passos existirão entre o valor inicial e final. A variável de simulação assumira cada um desses valores definidos pelos passos.

#### 8.3 SIMULAÇÃO PNOISE

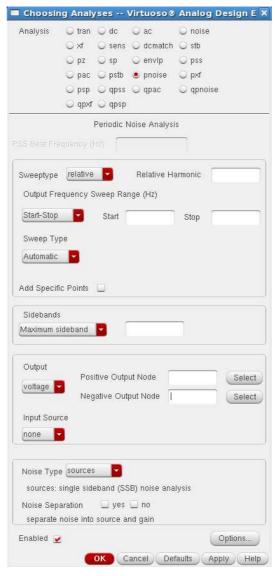

Essa simulação permite estimar o nível de ruído presente em uma determinada banda. Nesse trabalho desejou-se avaliar o nível de ruído ao redor do sinal gerado pelo VCO, ou seja, ao redor de 920MHz. Antes de realizar essa simulação, deve-se realizar a simulação PSS. A caixa de diálogo dessa simulação é mostrada na Figura 8.3.

Figura 8.3 – Caixa de dialogo da simulação PNOISE.

O primeiro ajuste que aparece é o "Sweeptype". Nesse ajuste define-se o tipo de analise a ser feita. Nesse trabalho, escolheu-se a opção *Relative*, a qual seleciona a frequência obtida na simulação PSS e analisa o ruído ao redor dessa frequência. No parâmetro "Output Frequency Sweep Range" define-se a faixa de valores onde se deseja estudar o ruído. Outro parâmetro

de importância é o "Maximum sideband", o qual deve receber um valor positivo, representando o múltiplo de frequência calculado pela simulação PSS a qual se deseja converter em frequência. O parâmetro "Input" informa ao simulador a fonte de ruído e o parâmetro "Output" indica a saída a ser estudada. Por último, ajusta-se o parâmetro "Noise type" para o tipo de ruído que se deseja estudar. Nesse trabalho optou-se pela opção *sources*.

#### 8.4 ROTINA PARA CÁLCULO DOS PARÂMETROS DO LF NO MATLAB

```

%ROTINA DE CÁLCULO DO LOOP FILTER

% parametros constantes

Fref = 16e6; %frequência de referência

Wref = 2*pi*Fref; %frequência angular

Ip = 20e-6; %corrente do charge pump N = 57.5; %divisor na saída do VCO

Kvco = 80e6; %ganho do VCO

§_____

% rotina de calculo

%_____

Bw = 0.1*Wref; %largura de banda = 1/10 frequência de referência

Wc = Bw; %frequência de corte

Wz = Wc/10 %frequência do zero (Wc/10 \le Wz \le Wc/4)

Wz2 = Wc/4

Wn = sqrt(Wc*Wz) %frequência natural

C1 = (Ip*Kvco)/((Wn^2)*2*pi*N); %primeiro capacitor do filtro

C2 = 0.1*C1; %segundo capacitor do filtro

R1 = (2*pi)/(Wz*C1); %resistor em série com C1

Qsi = (R1/2)*sqrt((Ip*Kvco*C1)/(N))

num = [(Kvco*Ip*R1) (Kvco*Ip)/C1];

den = [1 (Kvco*Ip*R1)/N (Kvco*Ip)/(C1*N)];

Wz = 1/(R1*C1)

G = tf(num, den)

step(num,den)

```